# **Caches**

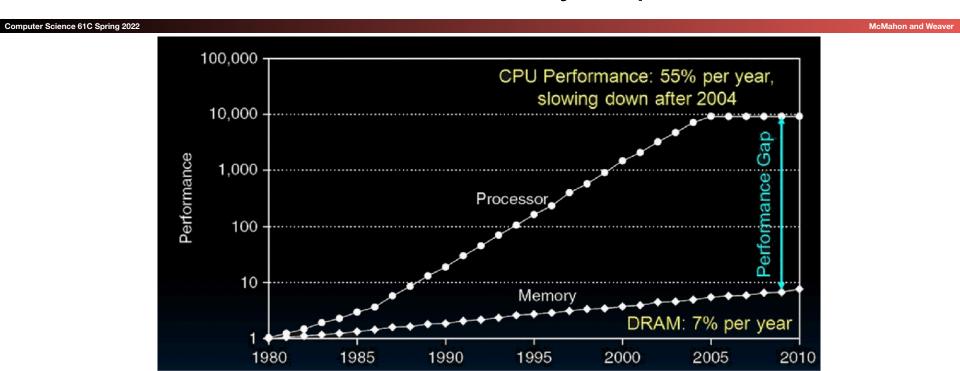

## Recall: Processor-DRAM Latency Gap

1980 microprocessor executes ~one instruction in same time as DRAM access 2020 microprocessor executes ~1000 instructions in same time as DRAM access

Berkeley EECS Slow DRAM access could have disastrous impact on CPU performance!

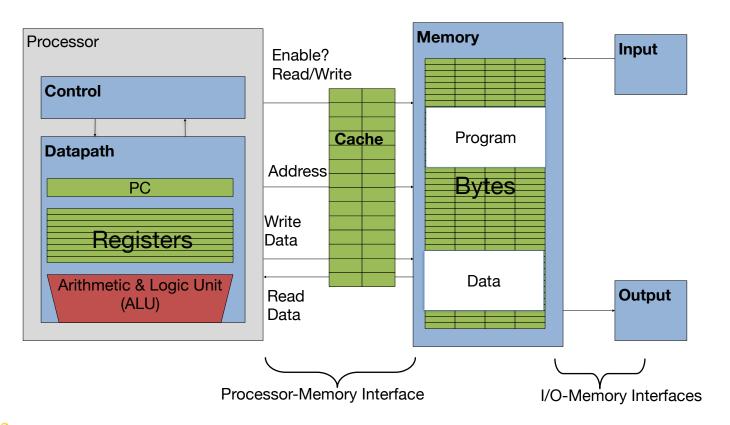

## Recall: Adding Cache to the Computer

Computer Science 61C Spring 2022

McMahon and Weaver

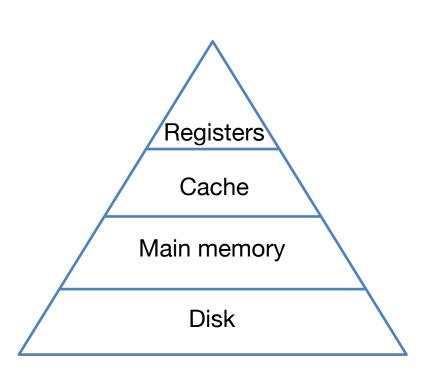

### Recall: Memory Hierarchy

Computer Science 61C Spring 2022

- If level closer to Processor, it is:

- Smaller

- Faster

- More expensive

- subset of lower levels (contains most recently used data)

- Lowest Level (usually disk=HDD/SSD) contains all available data

- Memory Hierarchy presents the processor with the illusion of a very large & fast memory

### Recall: Taking Advantage of Locality

Computer Science 61C Spring 2022 McMahon and Weave

### Temporal Locality

- If a memory location is referenced then it will tend to be referenced again soon

- ⇒ Keep most recently accessed data items closer to the processor

### Spatial Locality

- If a memory location is referenced, the locations with nearby addresses will tend to be referenced soon

- → Move blocks consisting of contiguous words closer to the processor

## Recall: Memory Access without Cache

Computer Science 61C Spring 2022

- Load word instruction: lw t0 0(t1)

- t1 contains 0x12F0 Memory[0x12F0] = 99

- 1. Processor issues address 0x12F0 to Memory

- 2. Memory reads word at address 0x12F0 (99)

- 3. Memory sends 99 to Processor

- 4. Processor loads 99 into register t0

### Recall: Memory Access with Cache

Computer Science 61C Spring 2022

- Load word instruction: lw t0,0(t1)

- t1 contains 0x12F0 Memory[0x12F0] = 99

- With cache: Processor issues address 0x12F0 to Cache

- 1. Cache checks to see if has copy of data at address 0x12F0 2a. If finds a match (Hit): cache reads 99, sends to processor 2b. No match (Miss): cache sends address 0x12F0 to Memory

- . Memory reads 99 at address 0x12F0

- II. Memory sends 99 to Cache

- III. Cache replaces word which can store 0x12F0 with new 99

- IV. Cache sends 99 to processor

- 2. Processor loads 99 into register t0

### Recall: Terminology

Computer Science 61C Spring 2022

- Cache Hit

- The data you were looking for is in the cache

- Cache Miss

- The data you were looking for is not in the cache

- Eviction

- Removing an entry from the cache

### **Terminology**

Computer Science 61C Spring 2022

- Hit Rate

- number of hits / number of accesses

- Miss Rate

- 1 hit rate

- Hit Time

- The time that it takes for you to access an item on a cache hit

- Miss penalty

- On a miss, the time it takes to access the block after discovering that its not in the cache

### Recall: Terminology

Computer Science 61C Spring 2022

McMahon and Weaver

#### Cache line/block

- The smallest unit of memory that can be transferred between the main memory and the cache

- Each line has its own entry in the cache

#### Line size/block size

The number of bytes in each cache line

### Capacity

- The total number of data bytes that can be stored in a cache

- For fully associative cache, capacity = # lines \* line size

Computer Science 61C Spring 2022 McMahon and Weaver

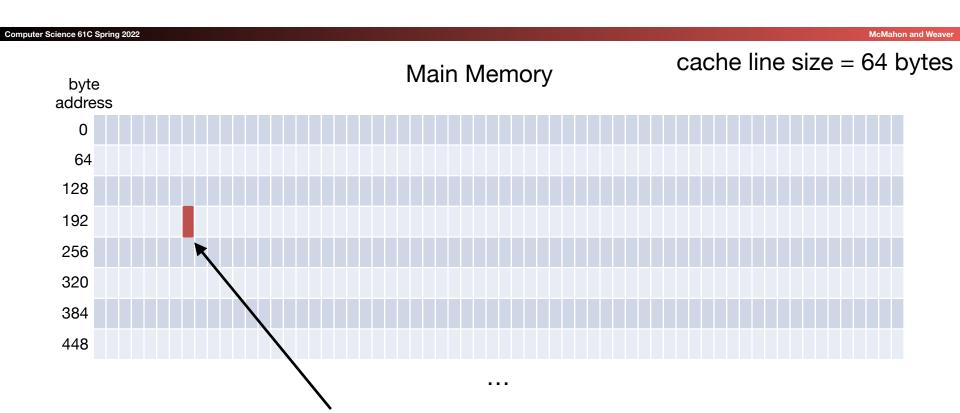

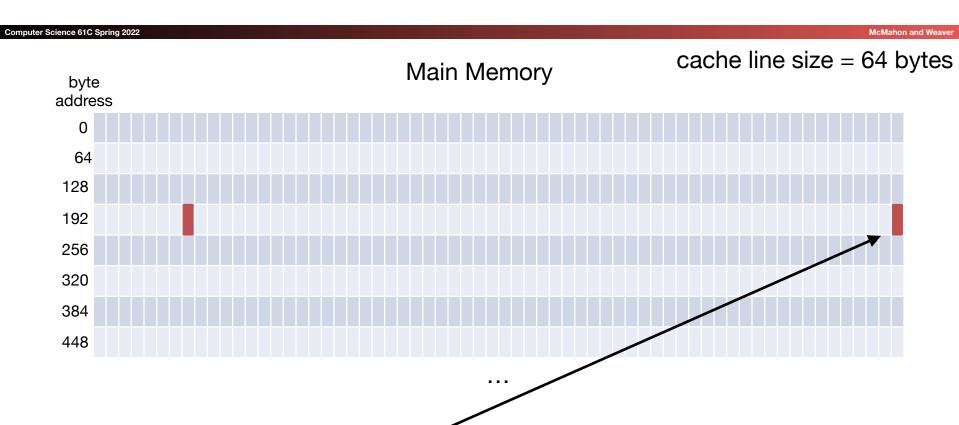

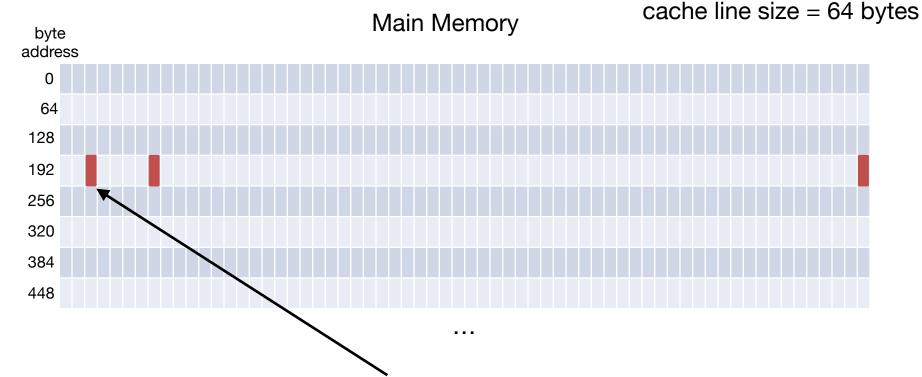

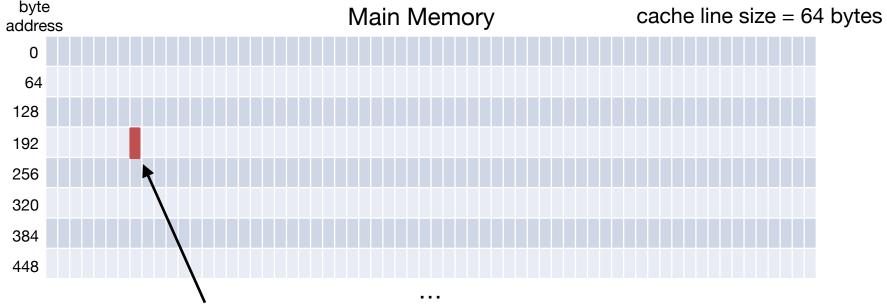

When we bring data from the main memory into the cache, it is done in the granularity of a cache line (or cache block)

- Typically cache lines are 64 bytes

- This helps us take advantage of spatial locality

If we want to access byte  $199_{10}$  and its not in the cache, we would bring in bytes  $80_{10}$   $192_{10}$   $255_{10}$  into the cache

If we then wanted to access byte  $255_{10}$ , we would get a cache hit because we just brought in the line that its in

If we then wanted to access byte  $194_{10}$ , we would get a cache hit because we just brought in the line that its in

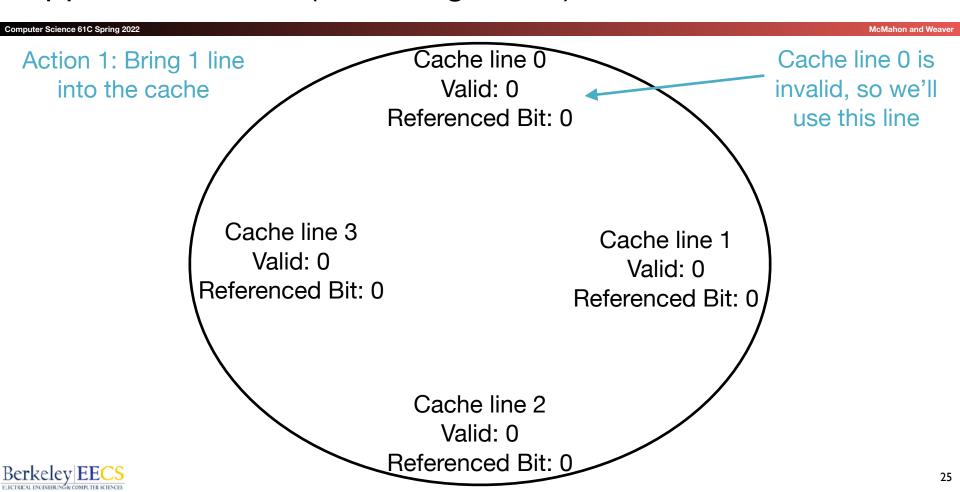

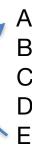

#### Recall: Valid Bit

Computer Science 61C Spring 2022

- When start a new program, cache does not have valid information for this program

- Need an indicator to tell if each entry is valid for this program

- 1 = valid

- 0 = invalid

### Recall: Tag

Computer Science 61C Spring 2022

McMahon and Weaver

Every line in the cache has a tag which helps us identify if the memory address that we are trying to access is stored in the cache

To check if our address matches a given line, we need to verify that the valid bit of that line is one and check if the tags are equivalent

### Recall: Write-through vs Write-back Policies

Computer Science 61C Spring 2022

### Write-through

- Write to the cache and the memory at the same time

- The write to memory will take longer

- Very simple to implement

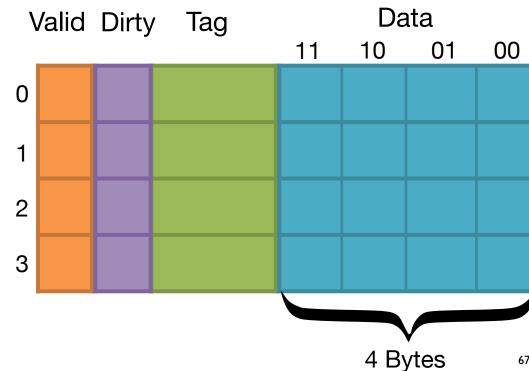

additional metadata

needed

#### Write-back

- Write data in cache and set the dirty bit to 1

- When this line gets evicted from the cache, write it to memory

- Typically lowers traffic to the memory because you might write to something multiple times before you evict it from the cache

#### Write-allocate vs No write-allocate

Computer Science 61C Spring 2022

- Write-allocate

- On a write miss, you bring the line into the cache and then update the line

- No write-allocate

- On a write miss, don't bring the line into the cache, you only update memory

- For both, you always bring the line in on a read miss

### **Common Combinations**

Computer Science 61C Spring 2022

McMahon and Weaver

- Write through, no write-allocate

- When there are write hits, the cache and main memory are updated

- On write misses, the block is not brought into the cache, and main memory is updated

- On read misses, the line is still brought into memory

- Write back, write-allocate

- On read and write misses, the line is brought into the cache

- On writes, you only update the cache and set the dirty bit to 1

#### Write allocate

Computer Science 61C Spring 2022

McMahon and Weave

When you write a byte, you'll read the whole line in from memory, store it

in the cache, and then update the byte

If we want to write to byte 199<sub>10</sub> and its not in the cache, we would bring in bytes 192<sub>10</sub>-255<sub>10</sub> into Berkeley EECS the cache and then update the byte

#### Recall: Eviction Policies

Computer Science 61C Spring 2022 McMahon and Weaver

- Least-Recently Used

- Replace the entry that has not been used for the longest time

- Hardware keeps track of access history

- Requires additional metadata

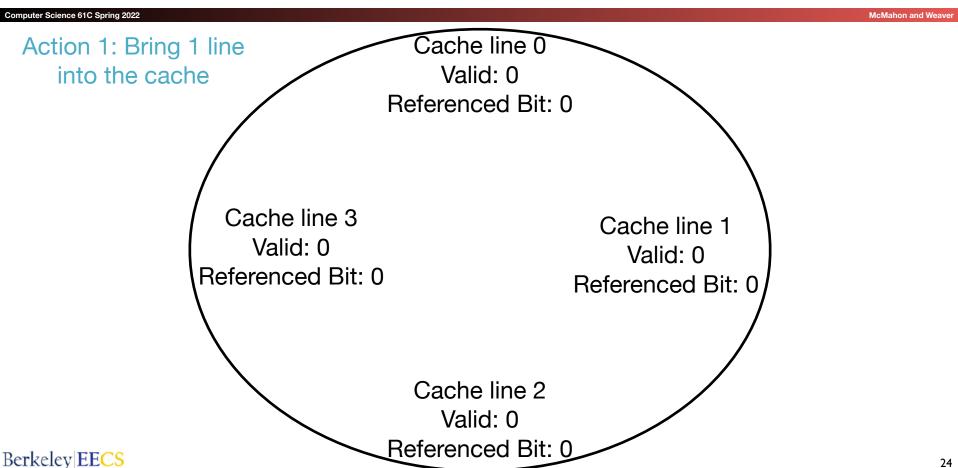

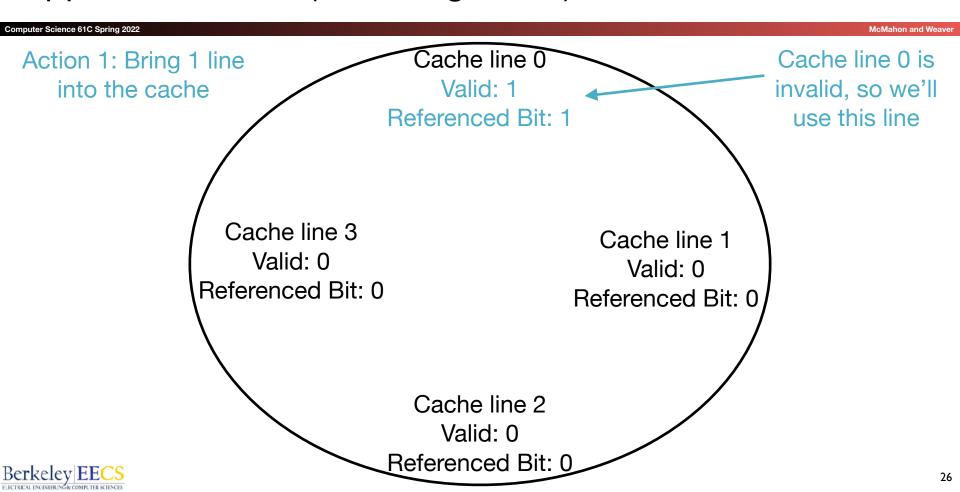

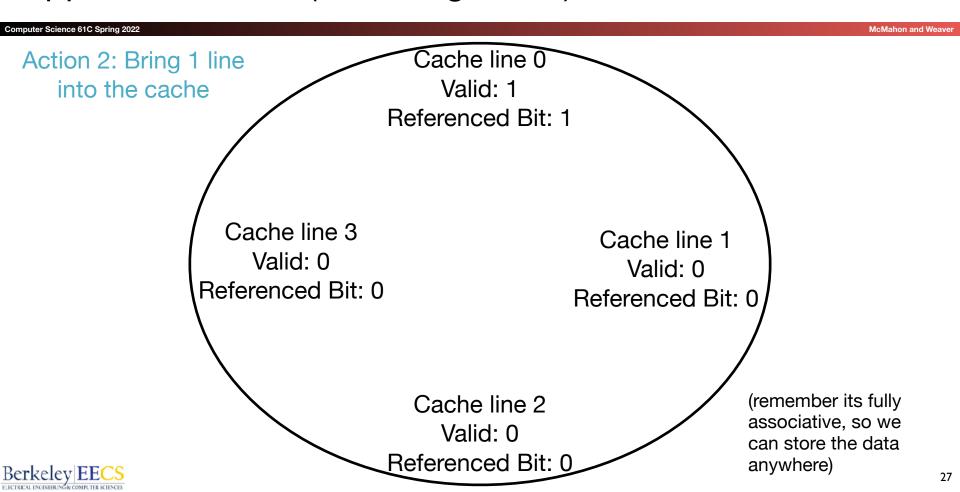

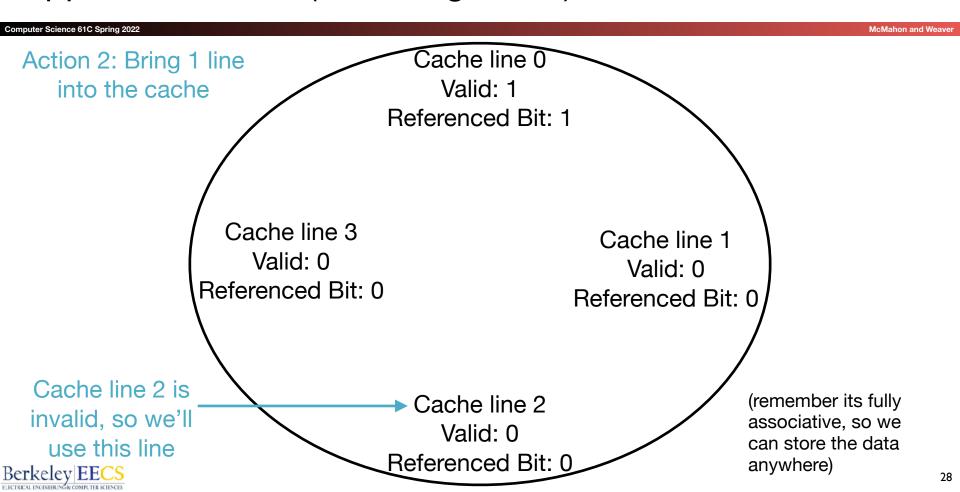

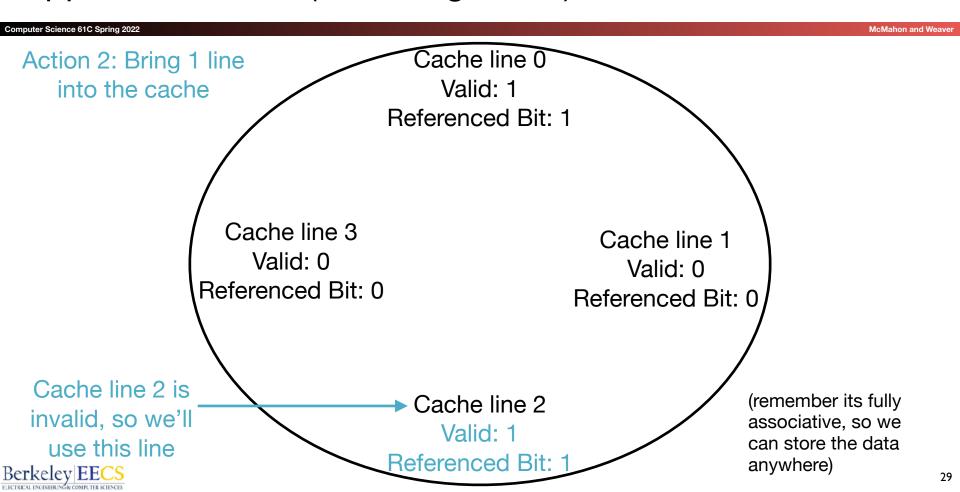

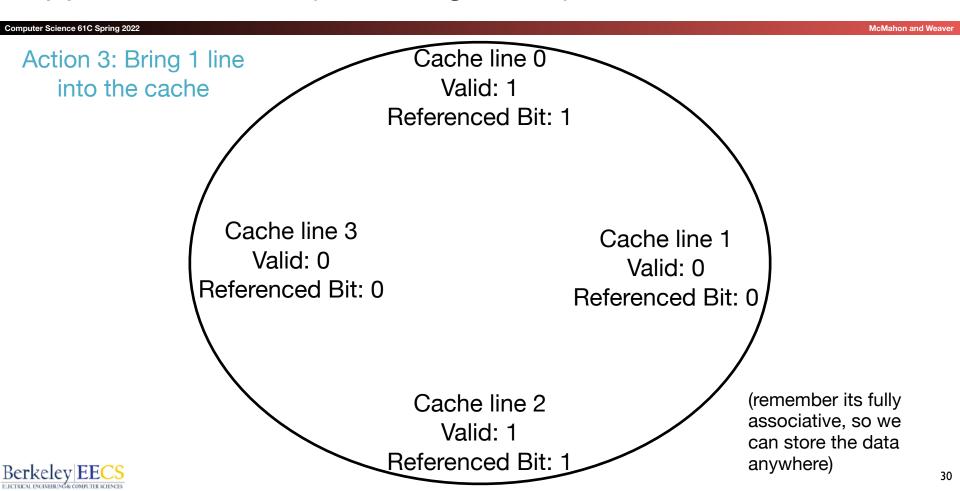

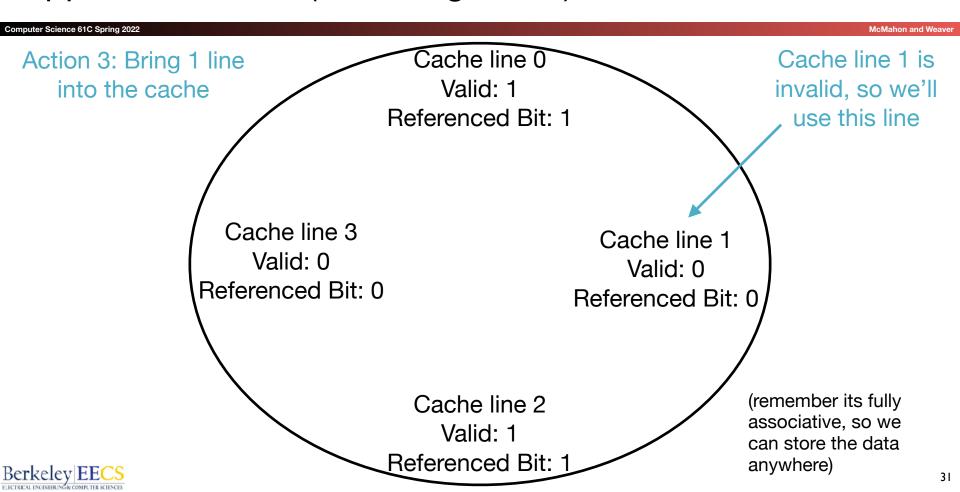

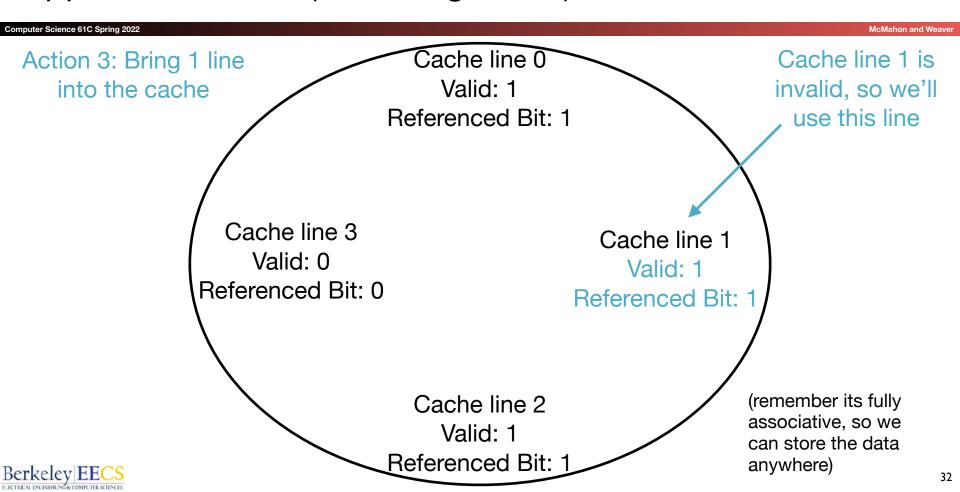

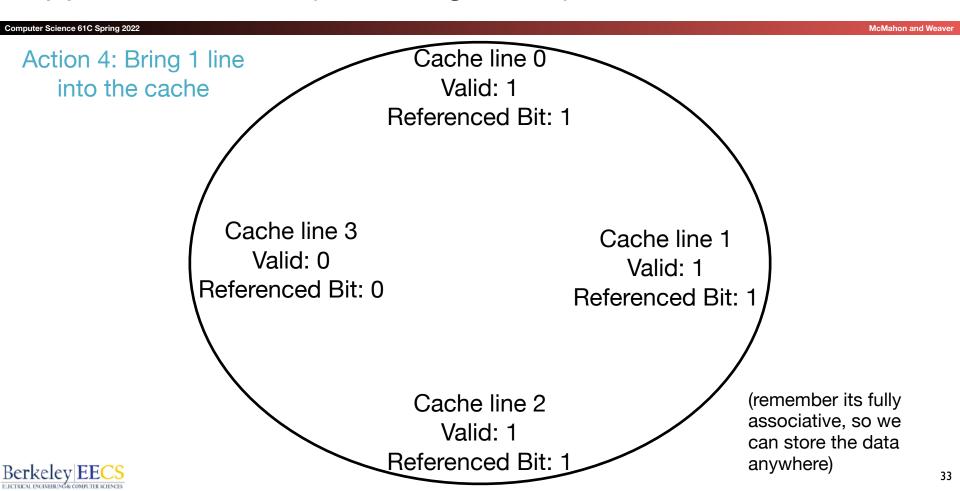

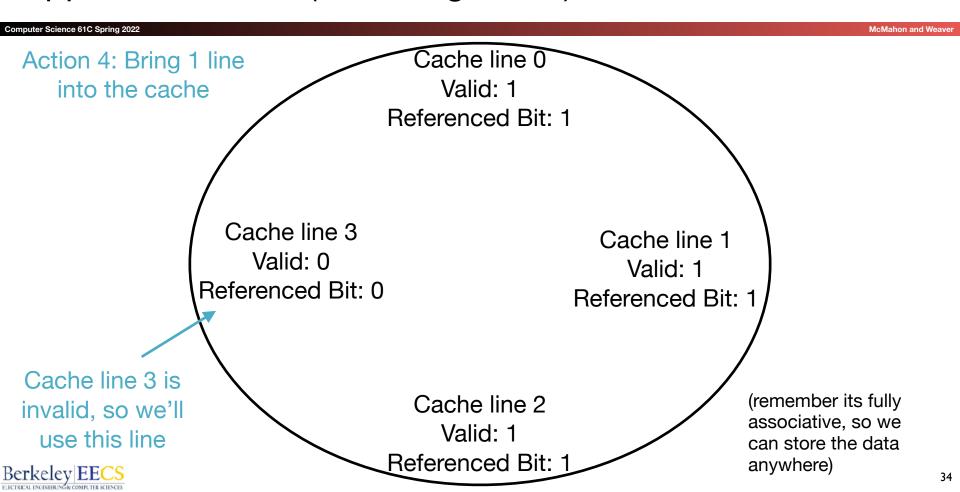

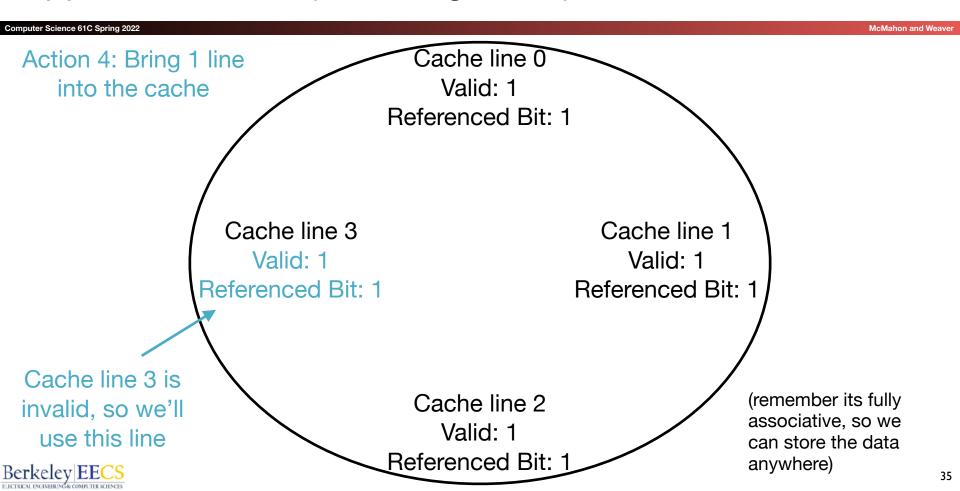

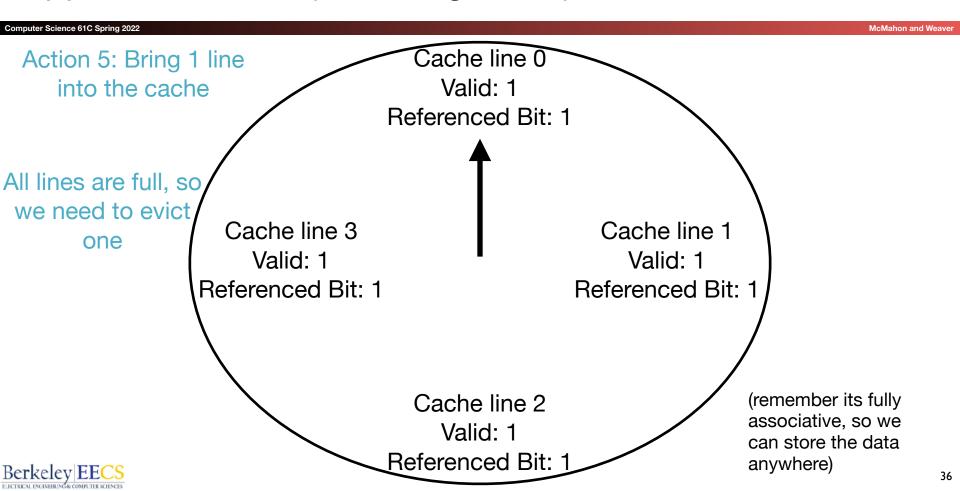

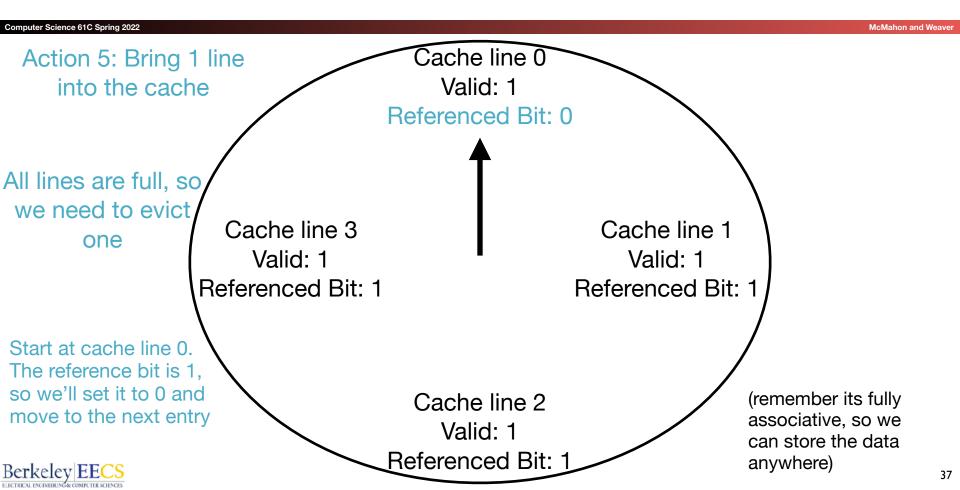

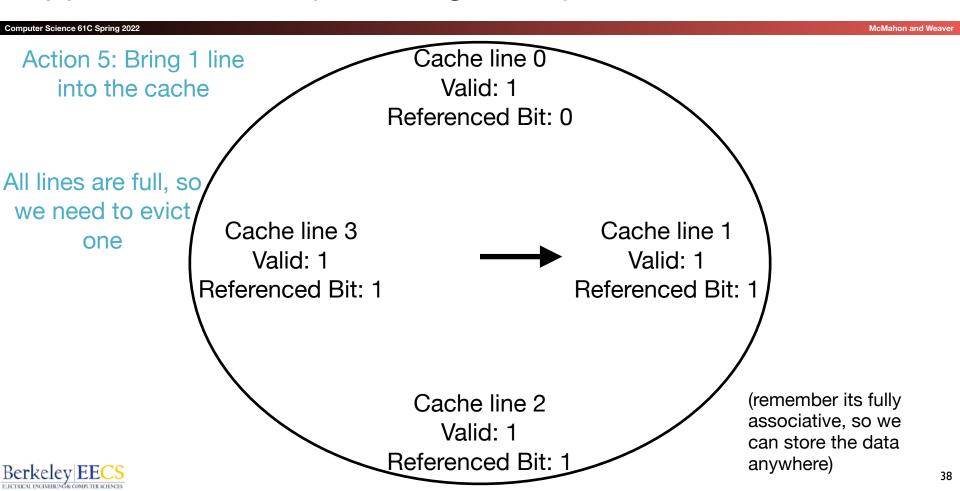

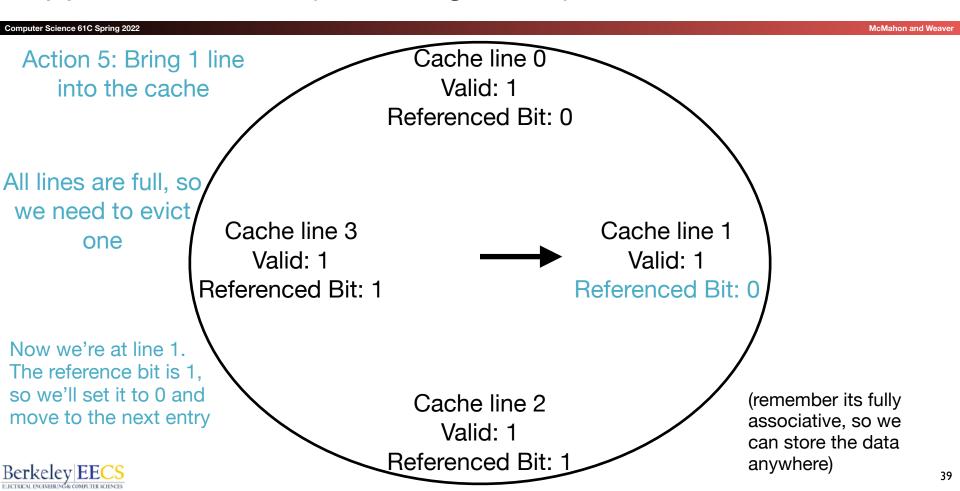

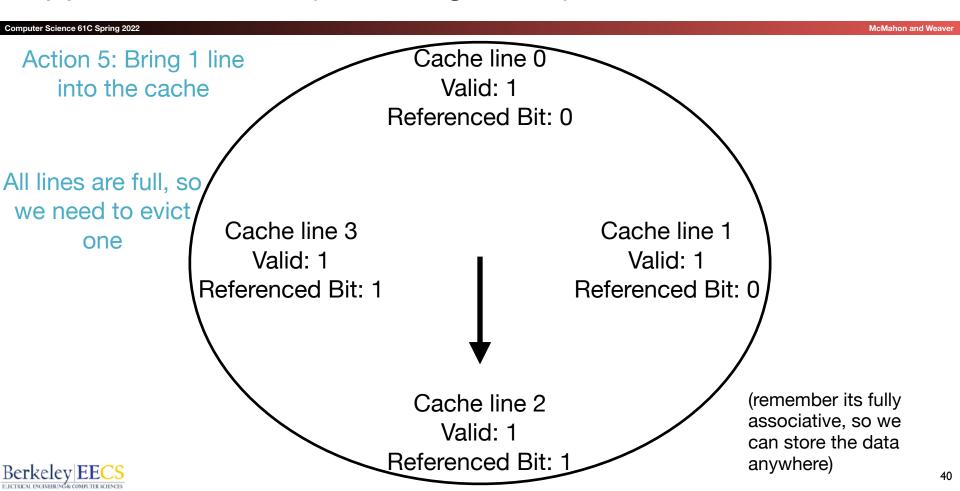

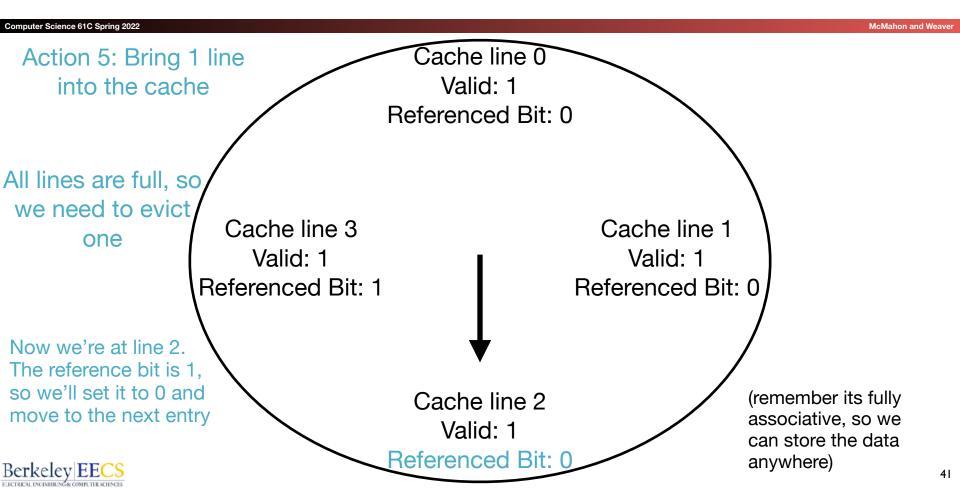

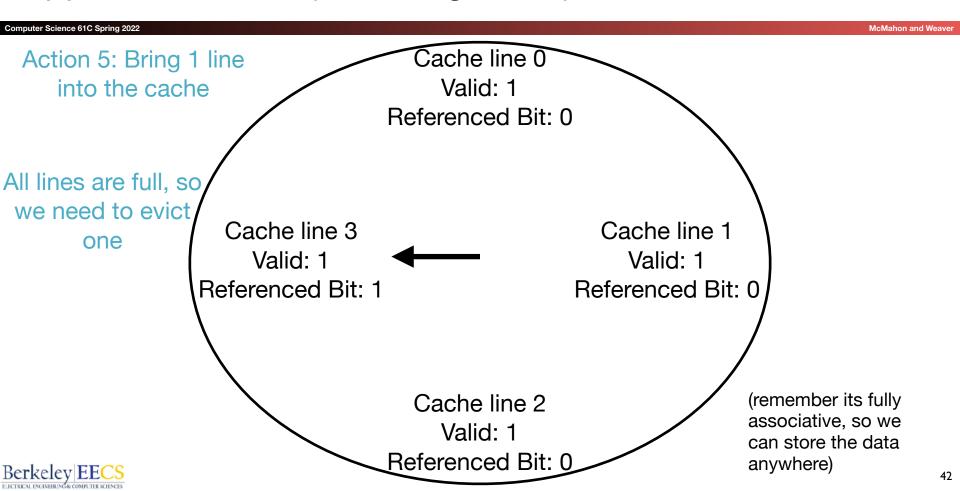

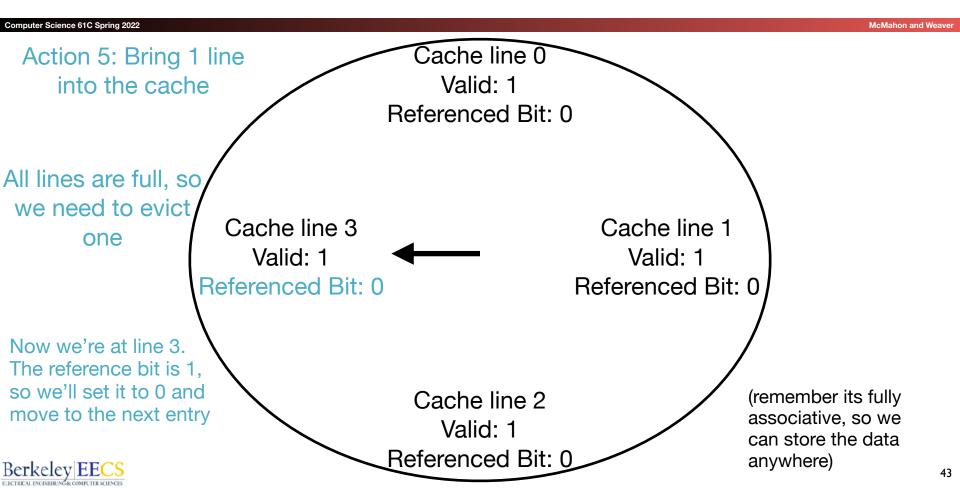

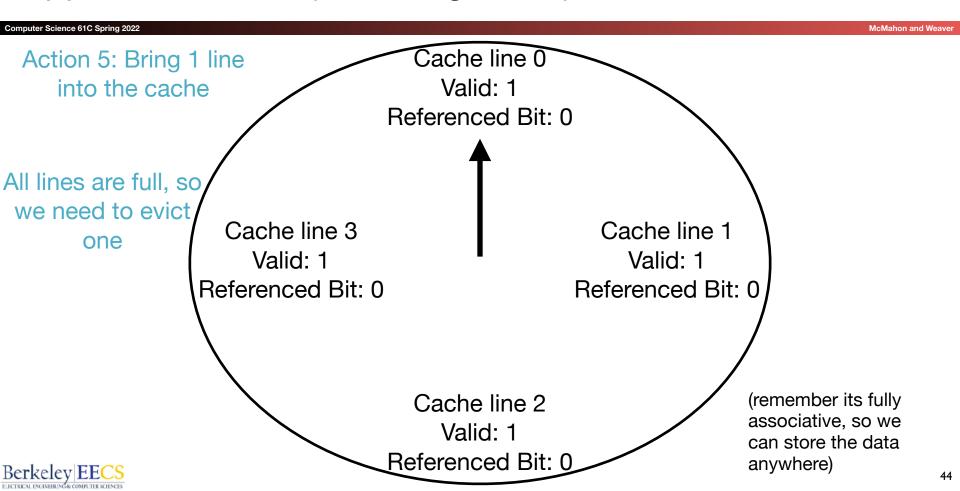

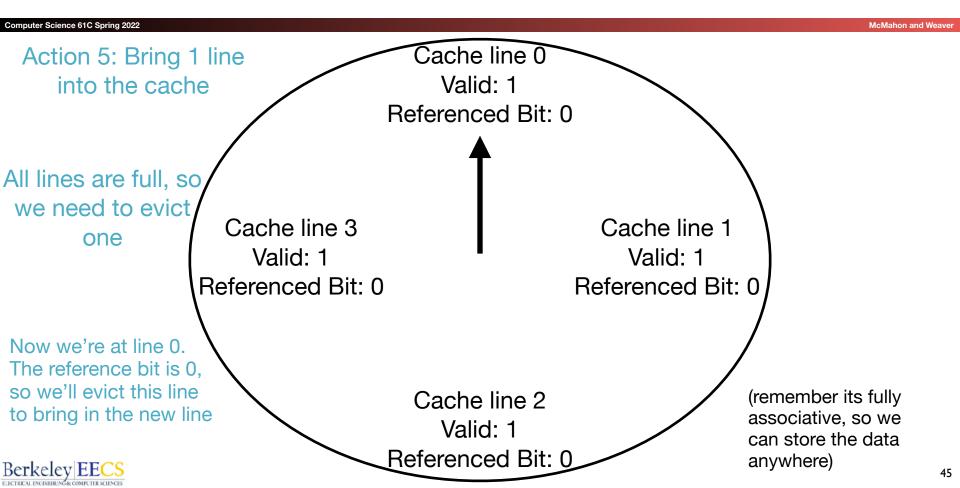

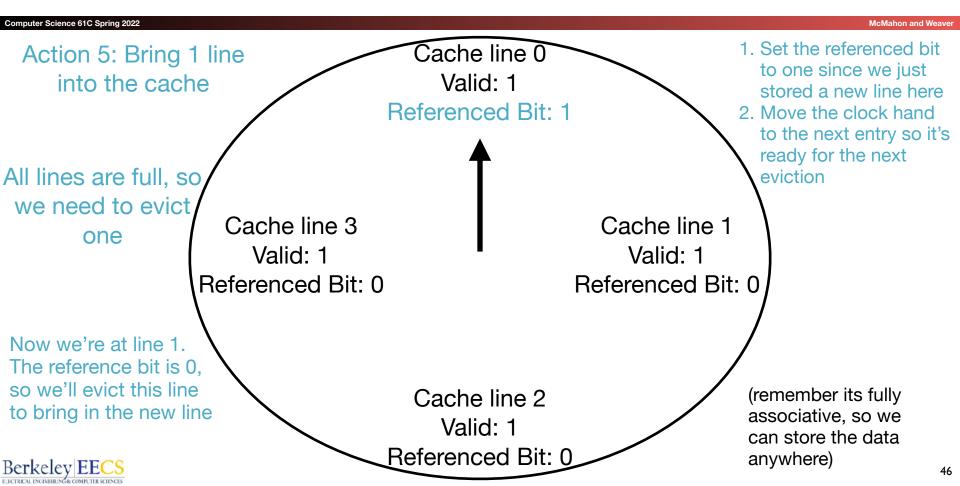

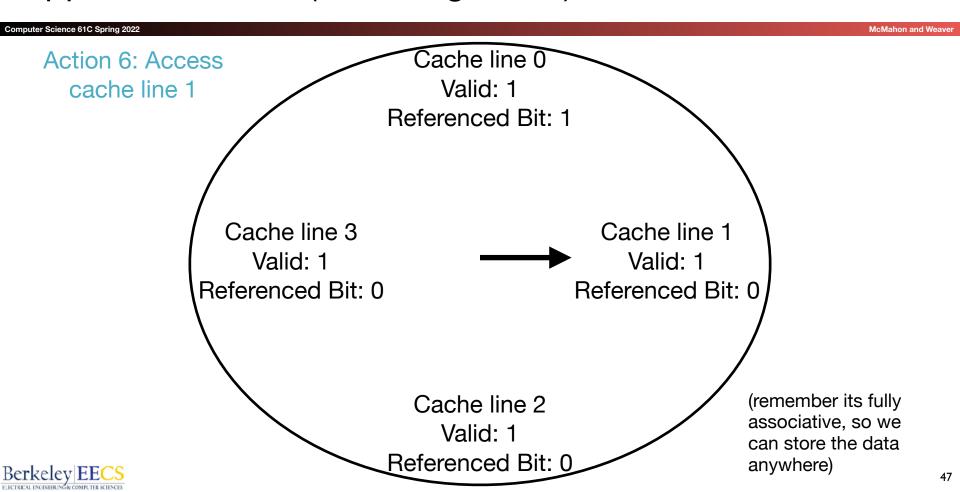

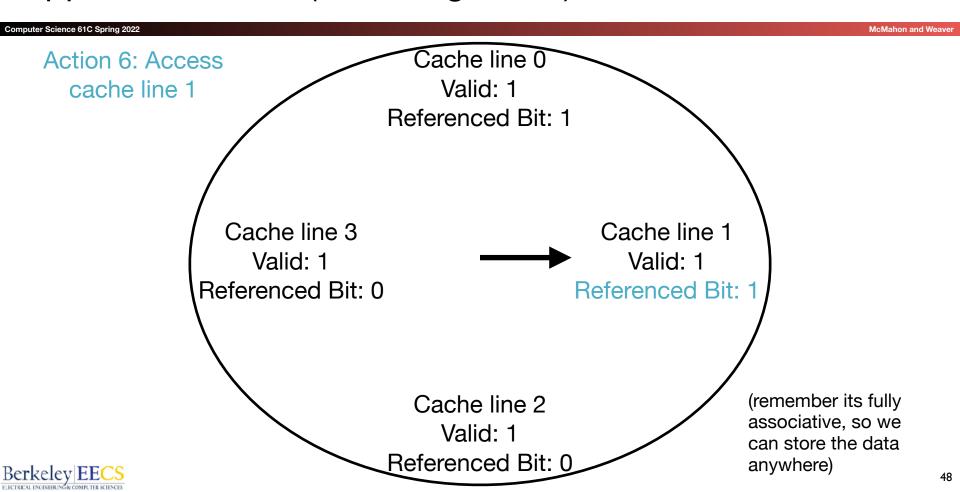

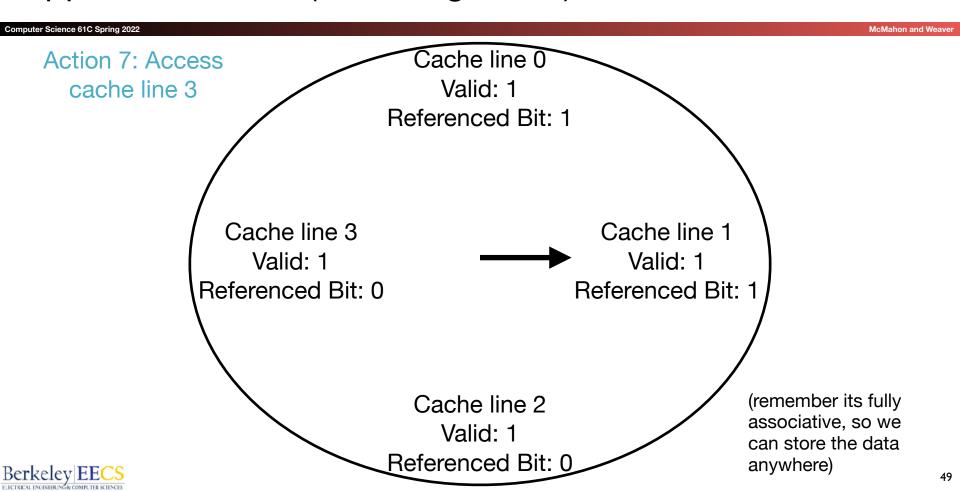

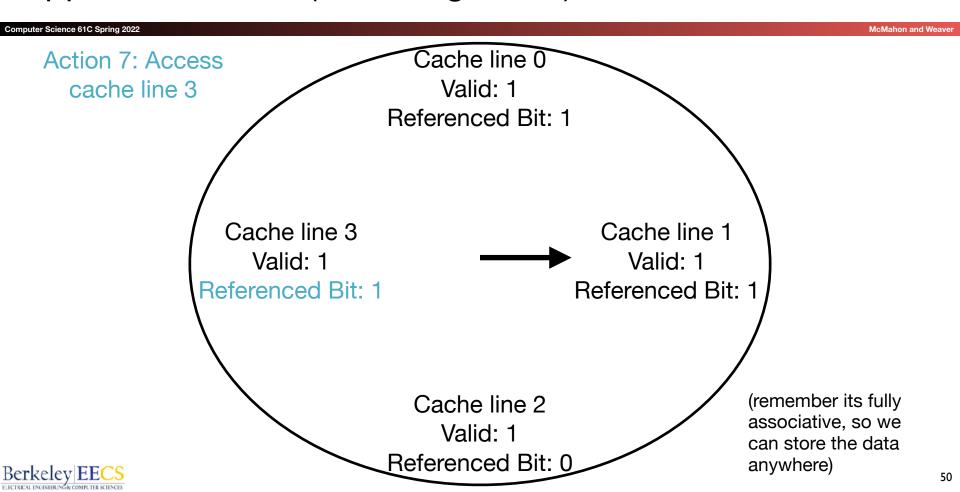

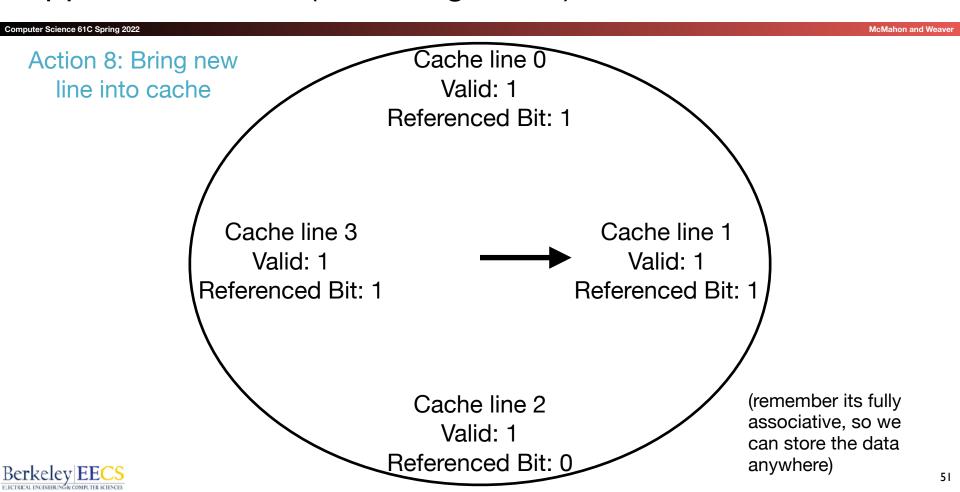

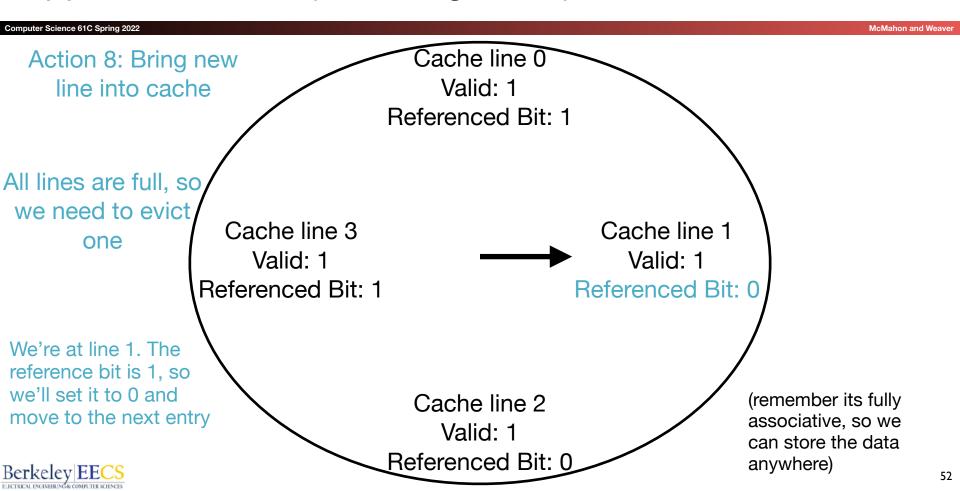

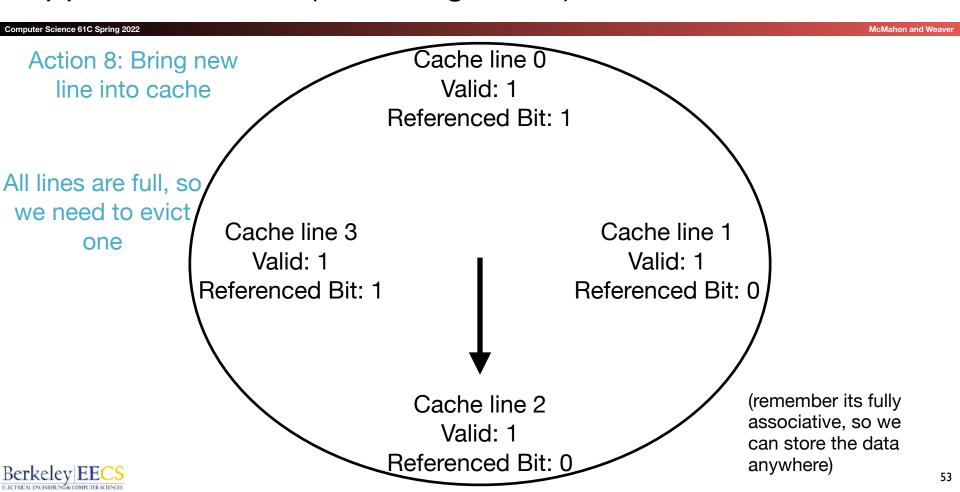

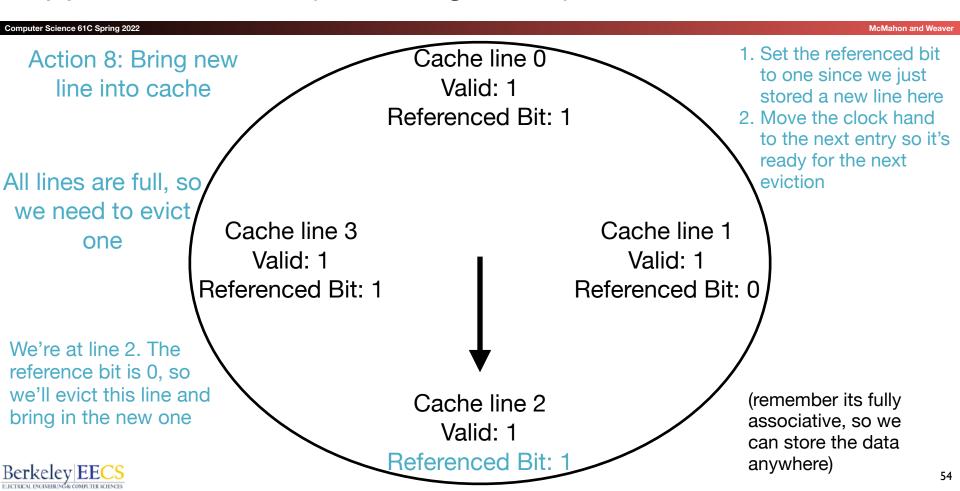

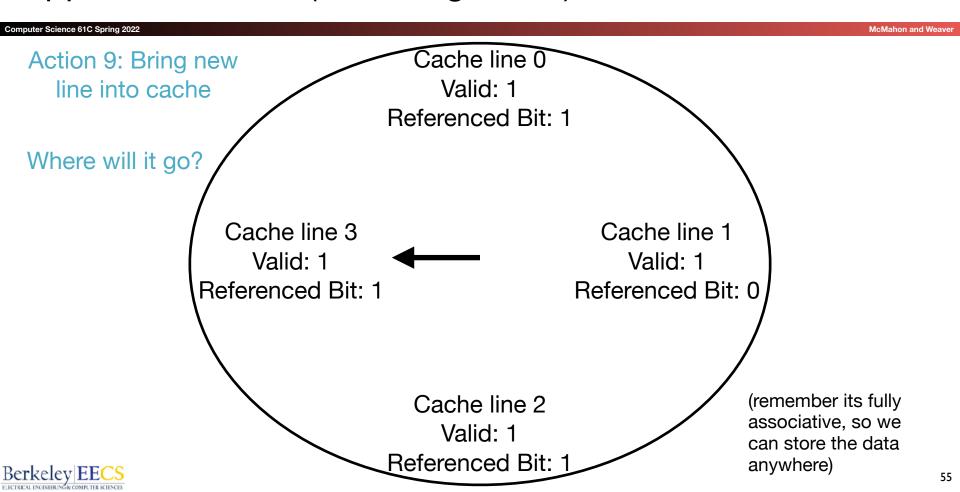

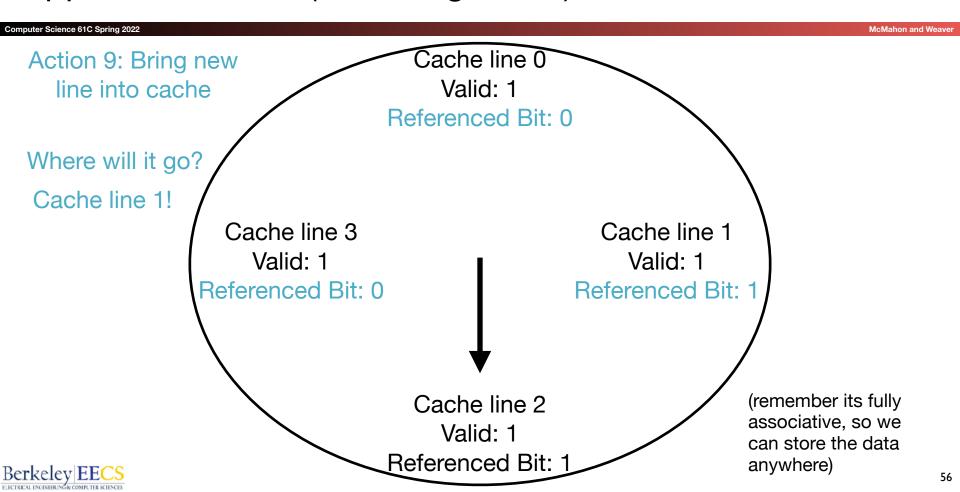

### Approximate LRU

Computer Science 61C Spring 2022

- Most caches have 100s or 1000s of lines

- Keeping track of the order in which each entry was accessed consumes a lot of bits and requires that you update every entry on each accesses

- Instead of implementing a true LRU algorithm, we implement an approximate LRU algorithm

Computer Science 61C Spring 2022

McMahon and Weaver

- Each cache line has 1 referenced bit

- This bit is set to 1 each time the line is accessed

- When a line needs to be evicted, we start at the first entry in the cache and check its referenced bit

- If the bit is 1, we set the bit to 0 and move to the next line

- If the bit is 0, we choose this line as the victim

- The next time we need to evict a line from the cache, we will start searching at the point where we left off

- (note that we don't start evicting lines until all entries in the cache are valid)

#### More Eviction Policies

Computer Science 61C Spring 2022

McMahon and Weaver

- Most recently used (MRU)

- Evict the line that was most recently used

- Random

- Chooses a random line to evict

- Benefit: don't have to keep track of additional metadata

- Example where these are better than LRU:

- 4 cache lines, iterating through an array where you access elements A, B, C, D, and E, where each element maps to a different line in the cache

- LRU would have a 0% hit rate

- MRU would have a 75 % hit rate

- Random would have a non-zero hit rate

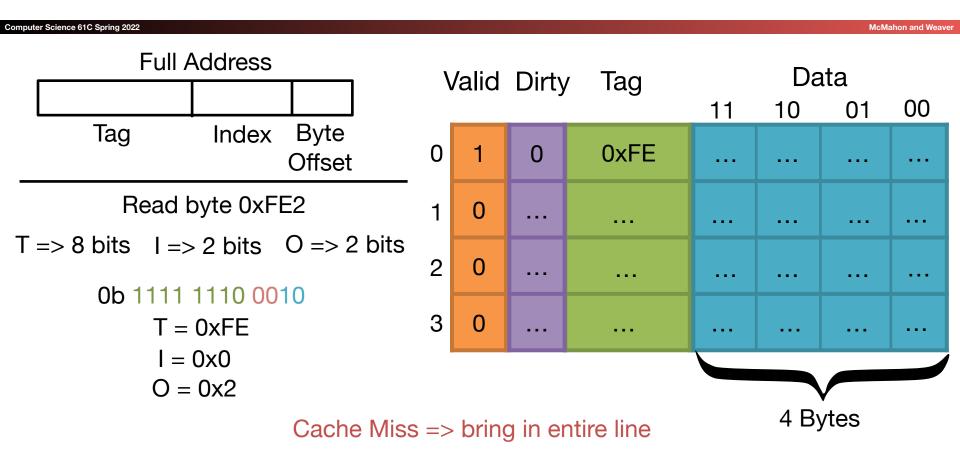

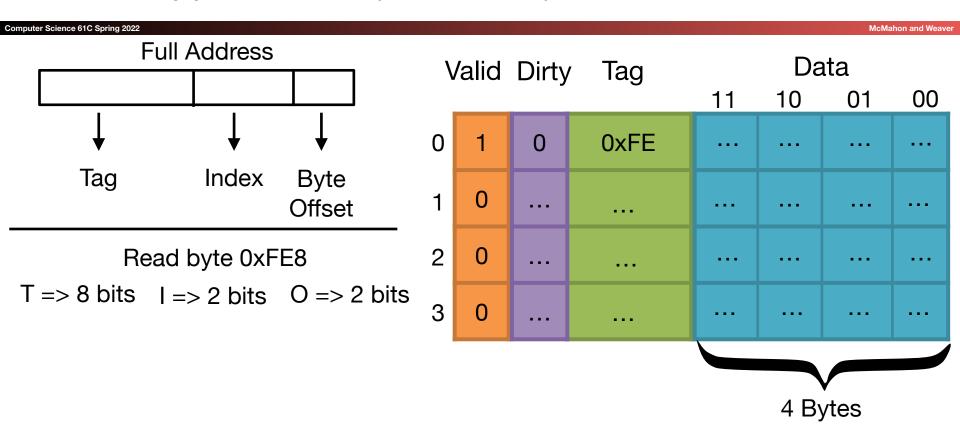

# **Fully Associative Cache**

#### Fully Associative Cache (write-back)

Computer Science 61C Spring 2022 McMahon and Weaver

The data can be stored anywhere

of room

Berkeley EEC

59

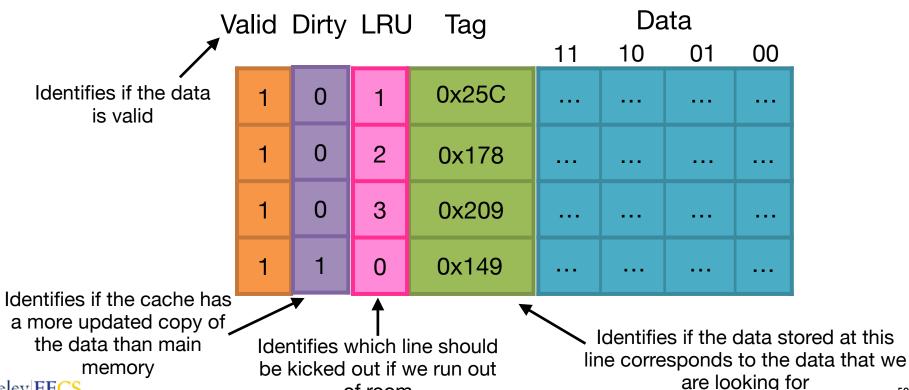

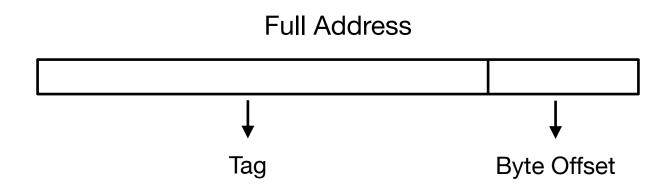

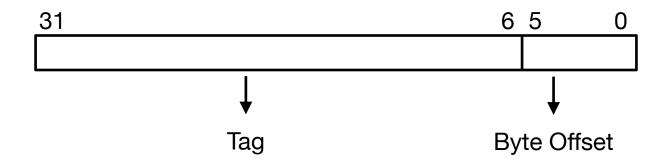

#### Address Breakdown

Computer Science 61C Spring 2022

McMahon and Weaver

# byte offset bits =  $log_2(line size)$

# tag bits = # address bits - # offset bits

#### **Example of Address Breakdown**

Computer Science 61C Spring 2022

McMahon and Weaver

Ex1: 64 KB fully associative cache with 16B blocks, 32-bit address space

# byte offset bits =

$$log_2(line size) = log_2(16) = 4$$

# tag bits = # address bits - # offset bits = 32 - 4 = 28

#### Example of Address Breakdown

Computer Science 61C Spring 2022

McMahon and Weaver

Ex2: 64 KB fully associative cache with 1K lines, 32-bit address space

```

line size = cache size / num lines = 64 KB / 1K = 64B

# byte offset bits = log<sub>2</sub>(line size) = log<sub>2</sub>(64) = 6

# tag bits = # address bits - # offset bits = 32 - 6 = 26

```

#### Hardware Required to Check for Hit

Computer Science 61C Spring 2022 McMahon and Weaver Address Tag Valid Data Tag Hit **◄**

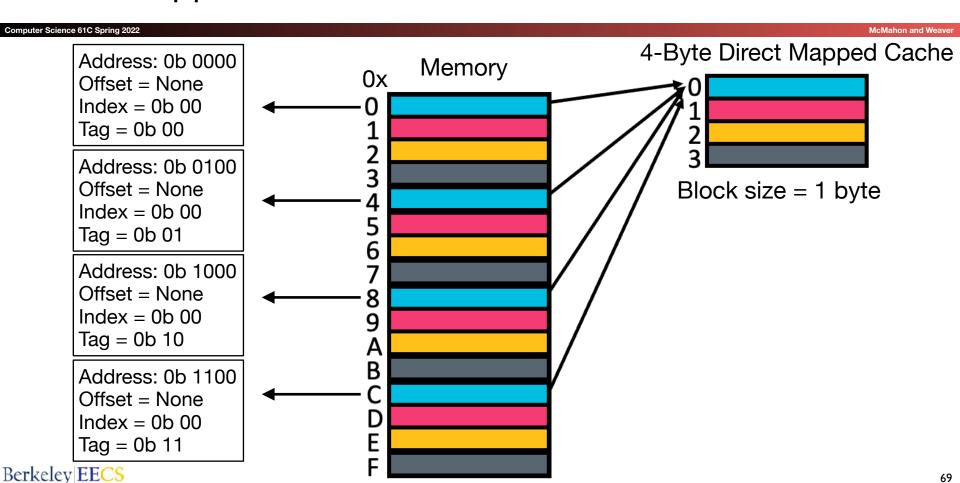

# **Direct Mapped Caches**

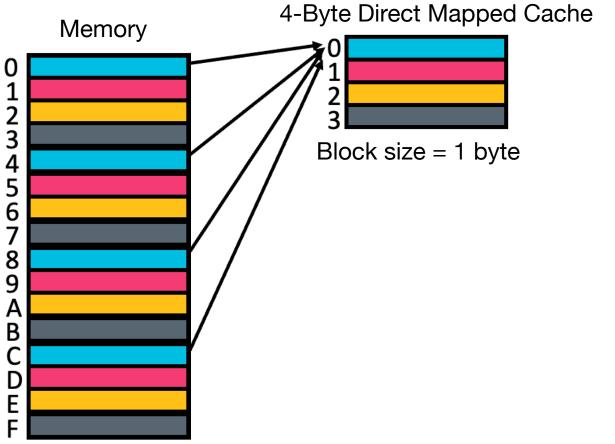

#### Direct Mapped Cache

Computer Science 61C Spring 2022

McMahon and Weaver

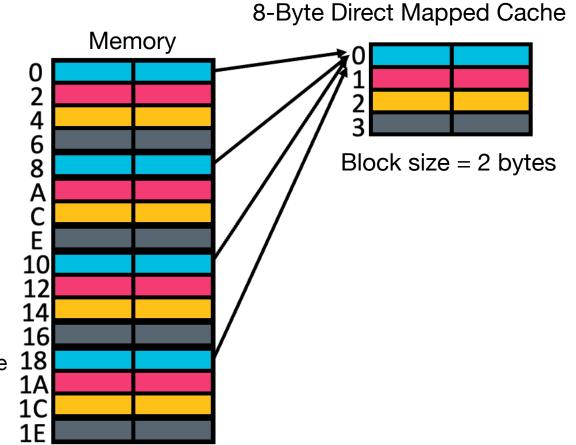

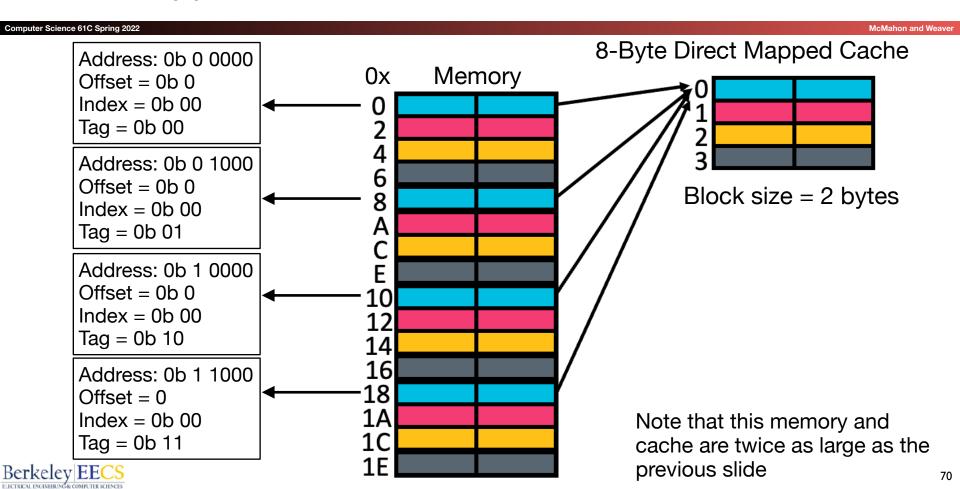

#### Direct Mapped Cache

Computer Science 61C Spring 2022

McMahon and Weaver

Note that this memory and cache are twice as large as the previous slide

#### Direct Mapped (write-back)

Computer Science 61C Spring 2022 McMahon and Weaver

The data can only be stored in one location

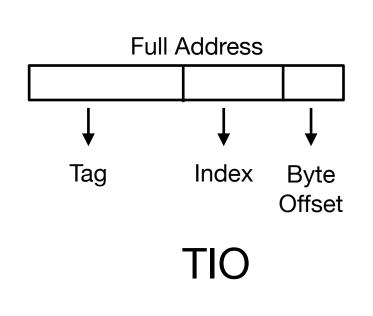

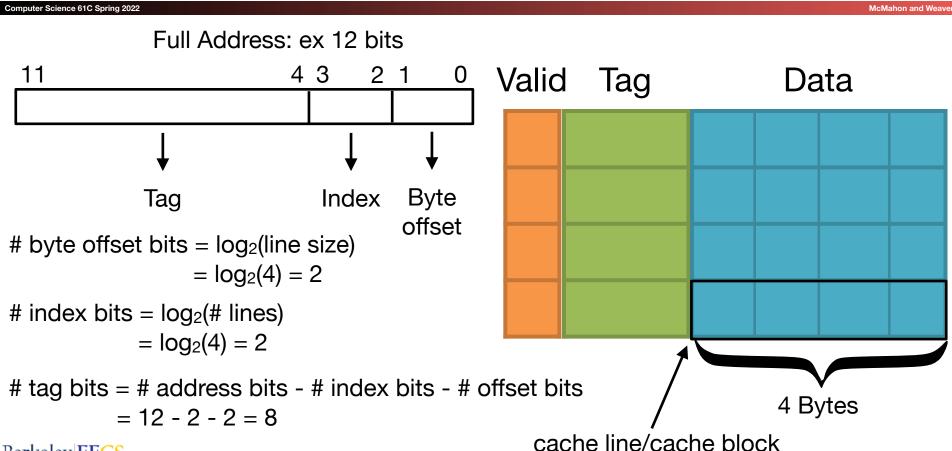

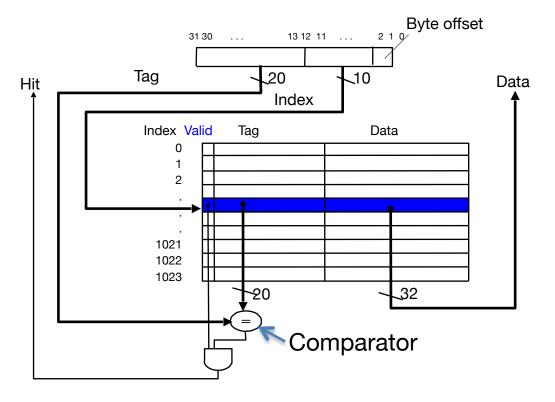

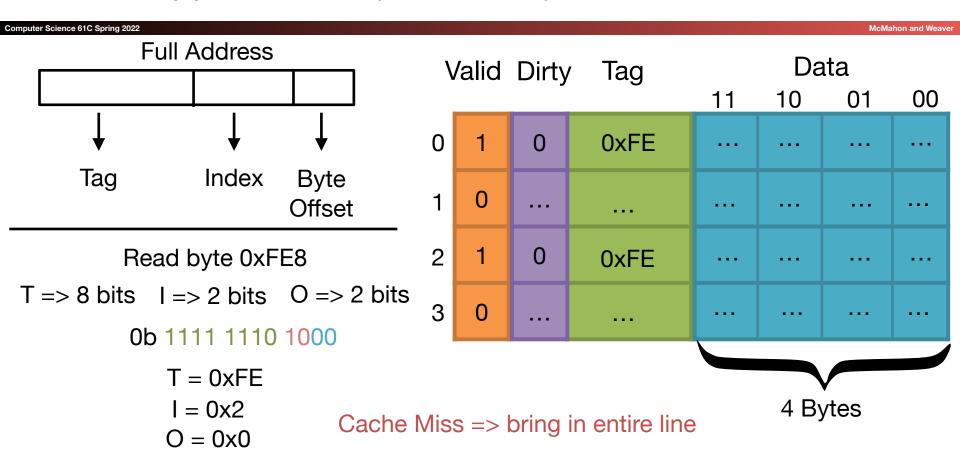

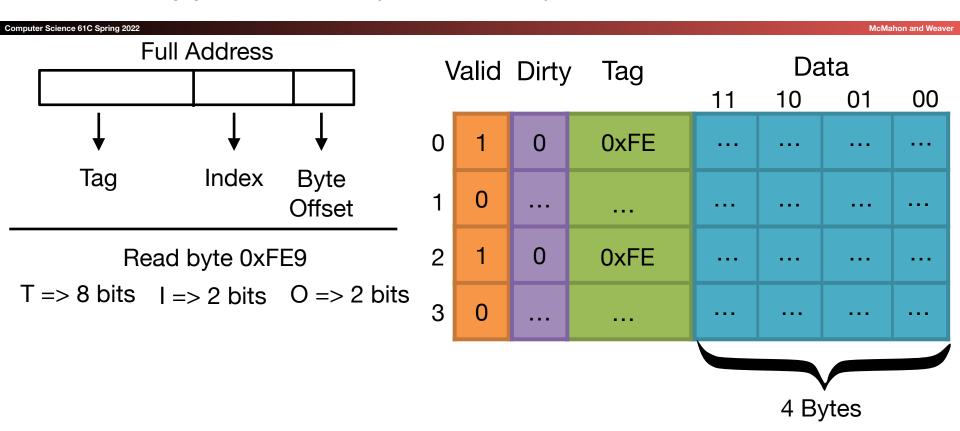

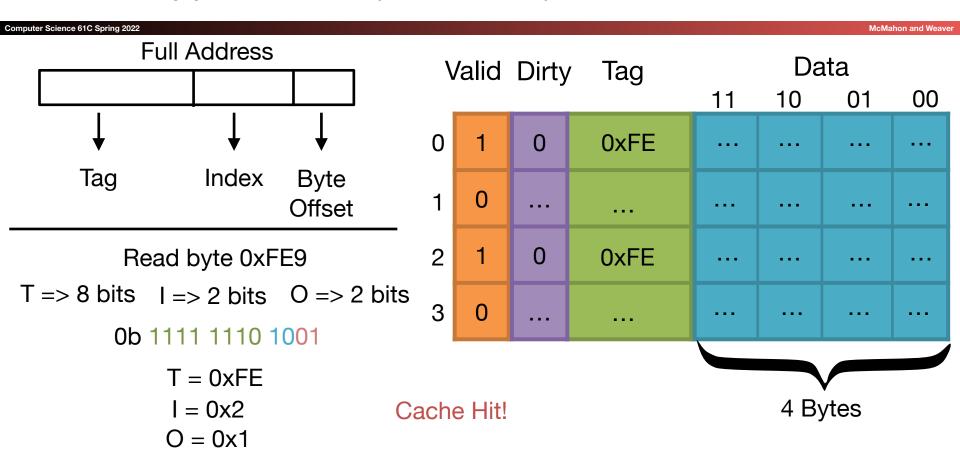

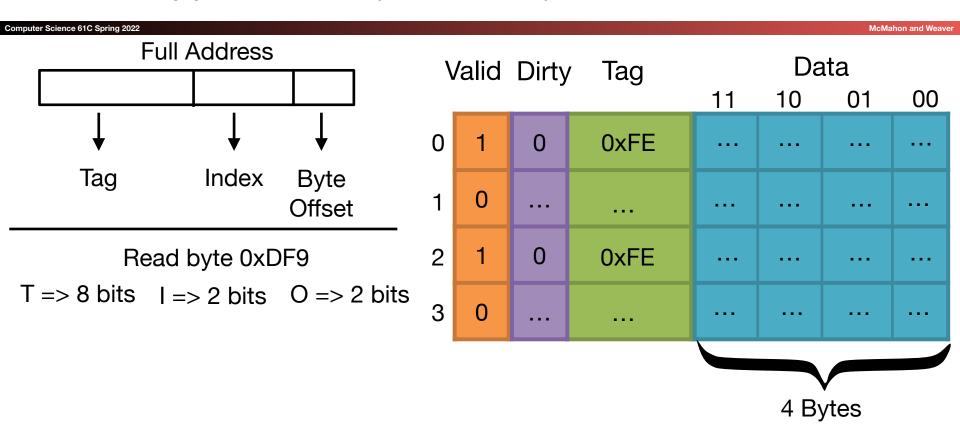

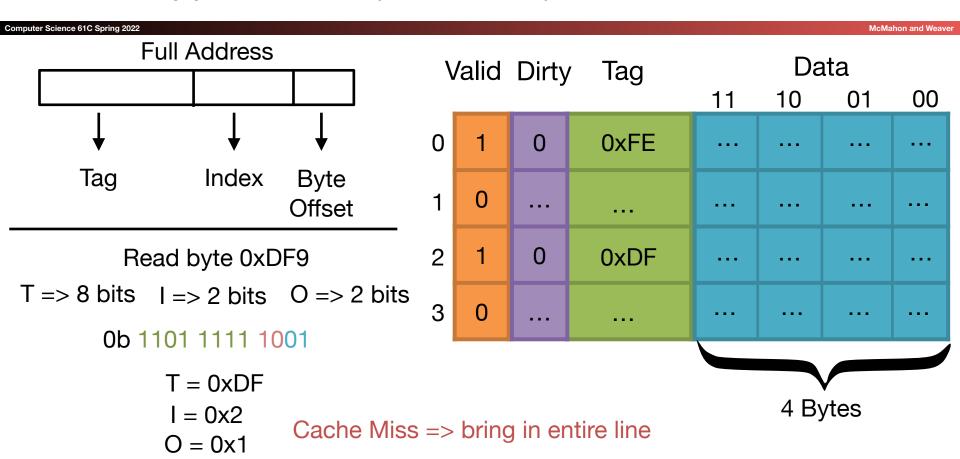

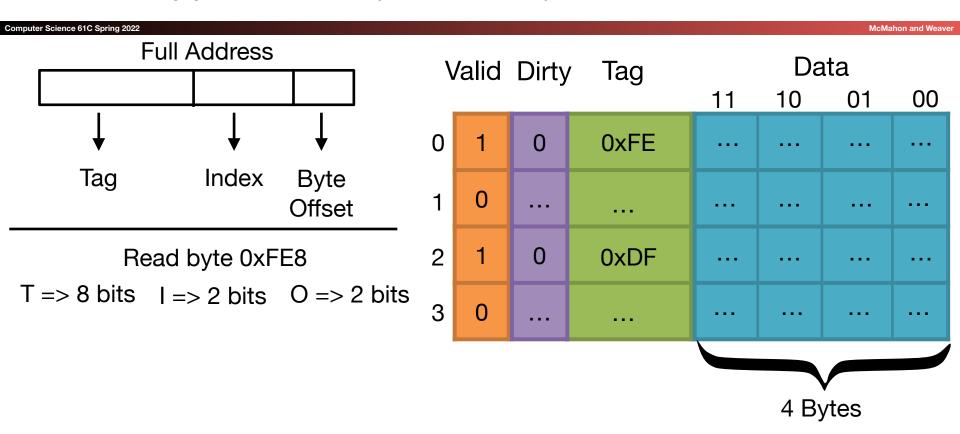

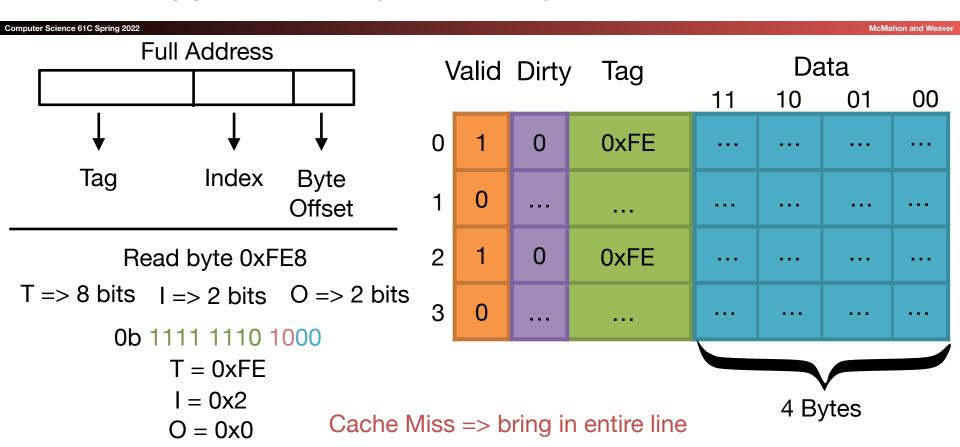

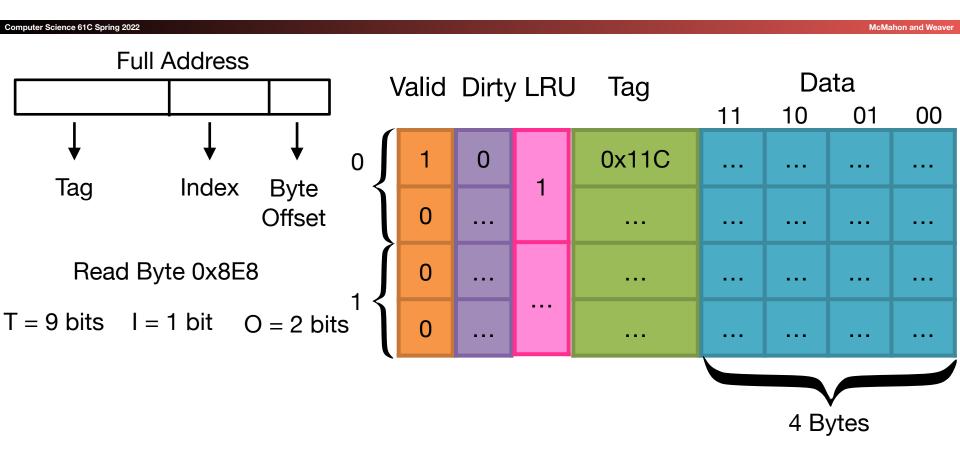

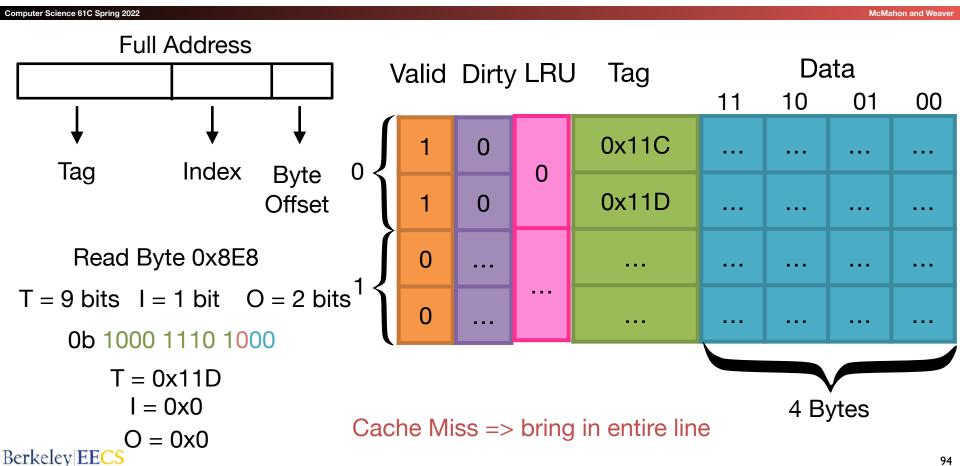

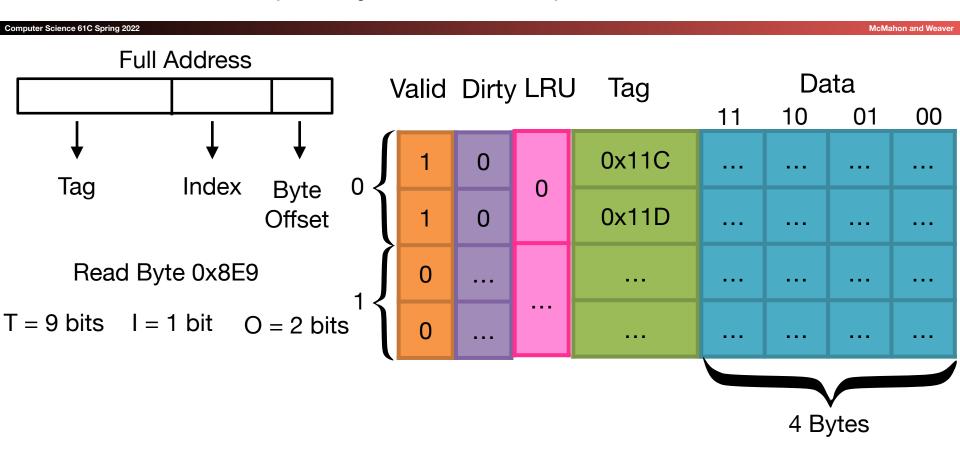

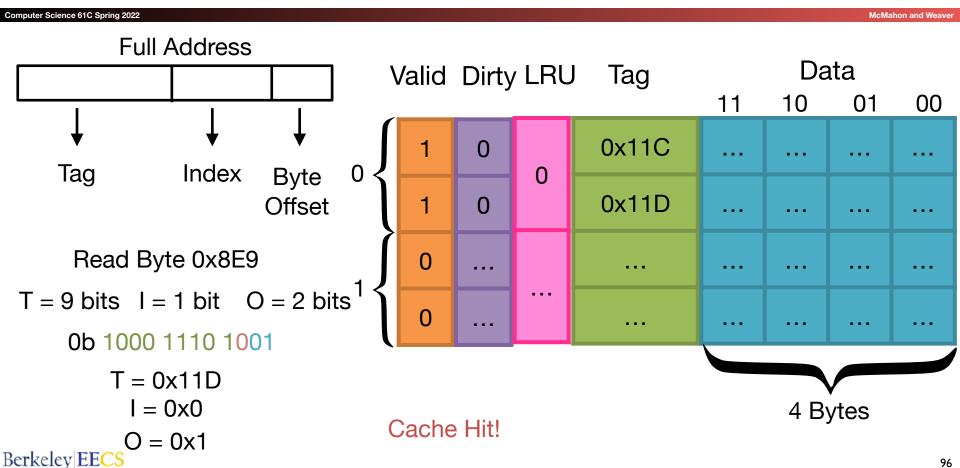

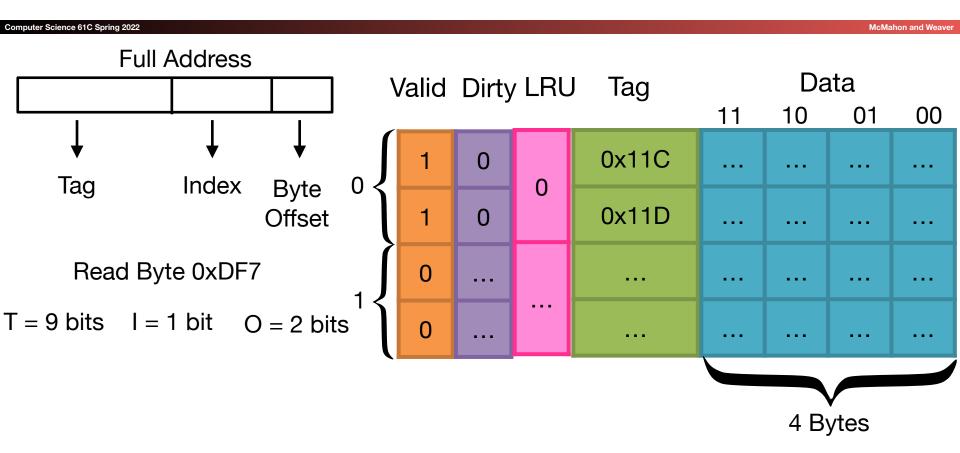

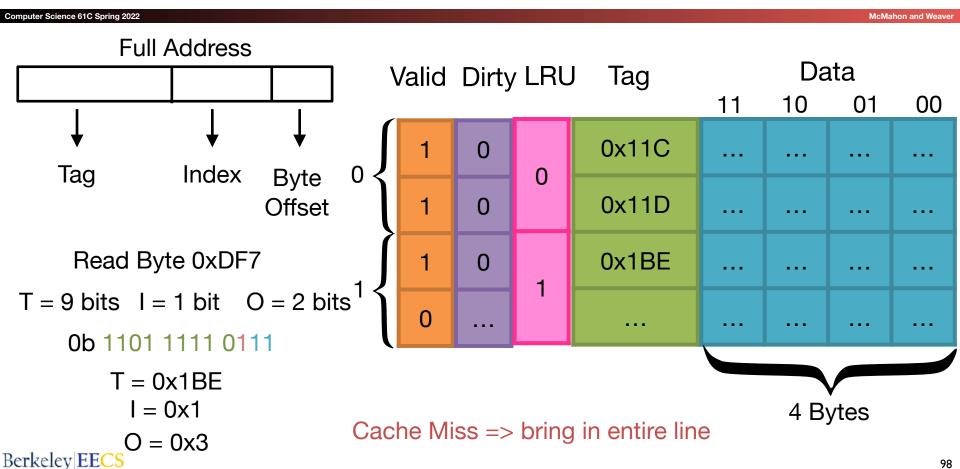

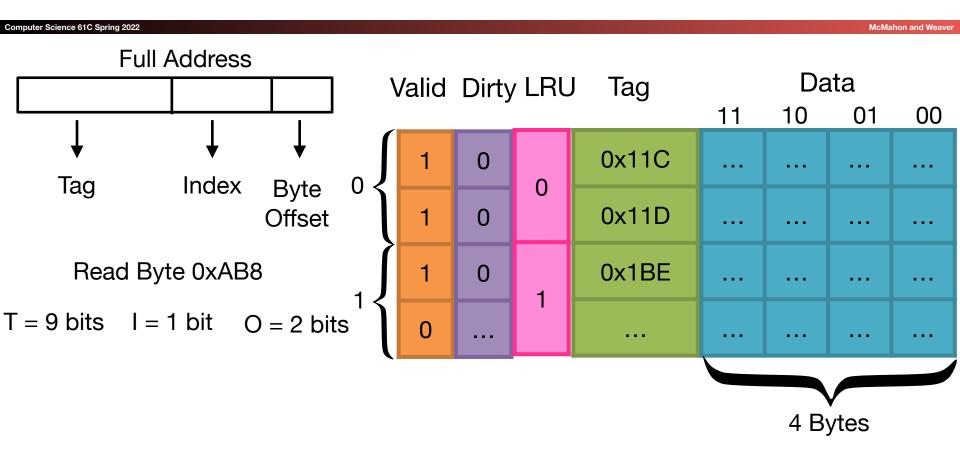

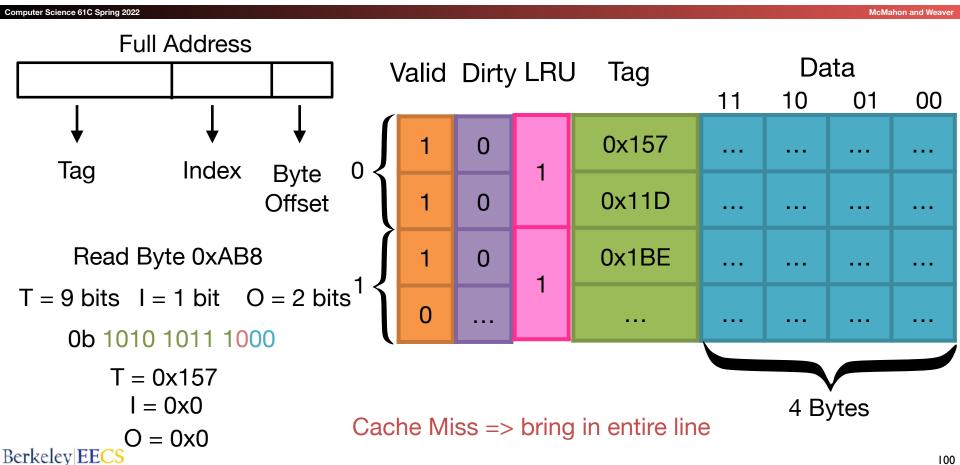

#### Direct Mapped Cache Address Breakdown

#### Direct Mapped Cache

#### Direct Mapped Cache

#### Direct Mapped Cache Address Breakdown

Computer Science 61C Spring 2022

McMahon and Weaver

```

# byte offset bits = log<sub>2</sub>(line size)

# index bits = log<sub>2</sub>(# lines)

# tag bits = # address bits - # index bits - # offset bits

```

Ex: Direct Mapped Cache with 32 bit address, 4B blocks and 4KB data

```

# byte offset bits = log_2(line size) = log_2(4) = 2

# lines = cache size / line size = 4KB / 4B = 1K

# index bits = log_2(# lines) = log_2(1K) = 10

# tag bits = # address bits - # index bits - # offset bits = 32 - 10 - 2 = 20

```

#### Direct-Mapped Cache Hardware: 4B blocks, 4KB data

Computer Science 61C Spring 2022 McMahon and Weaver

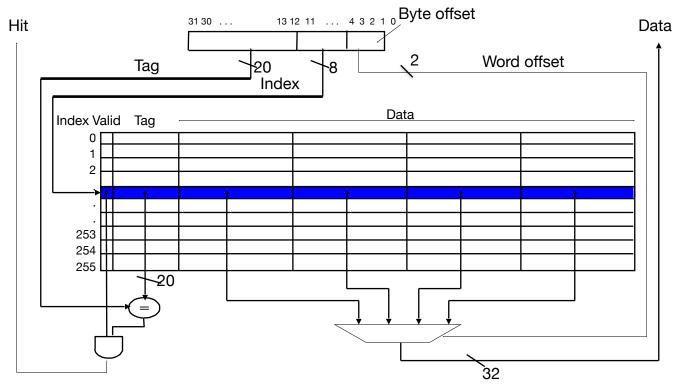

#### Direct Mapped Cache Address Breakdown

Computer Science 61C Spring 2022

McMahon and Weaver

```

# byte offset bits = log<sub>2</sub>(line size)

# index bits = log<sub>2</sub>(# lines)

# tag bits = # address bits - # index bits - # offset bits

```

Ex: Direct Mapped Cache with 32 bit address, 16B blocks and 4KB data

```

# byte offset bits = log_2(line size) = log_2(16) = 4

# lines = cache size / line size = 4KB / 16B = 256

# index bits = log_2(# lines) = log_2(256) = 8

# tag bits = # address bits - # index bits - # offset bits = 32 - 8 - 4 = 20

```

#### Multiword-Block Direct-Mapped Cache: 16B block size, 4 kB data

Computer Science 61C Spring 2022

McMahon and Weaver

#### Direct Mapped Cache Replacement

Computer Science 61C Spring 2022 McMahon and Weaver

Every address can only be stored at one location in the cache

If there is already something else stored at our index, we must evict it

#### Direct Mapped

Computer Science 61C Spring 2022

If we had used a fully associative cache, the previous access would have been a hit!

- Direct Mapped leads to more conflicts than fully associative

- Compromise: Set Associative

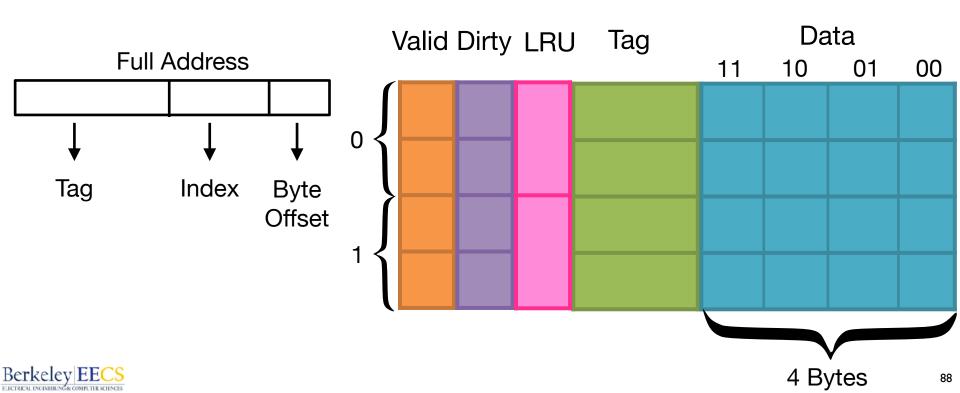

# **Set Associative Caches**

Computer Science 61C Spring 2022 McMahon and Weaver

The data can only be stored at one index, but there are multiple slots to store it in

Computer Science 61C Spring 2022

McMahon and Weaver

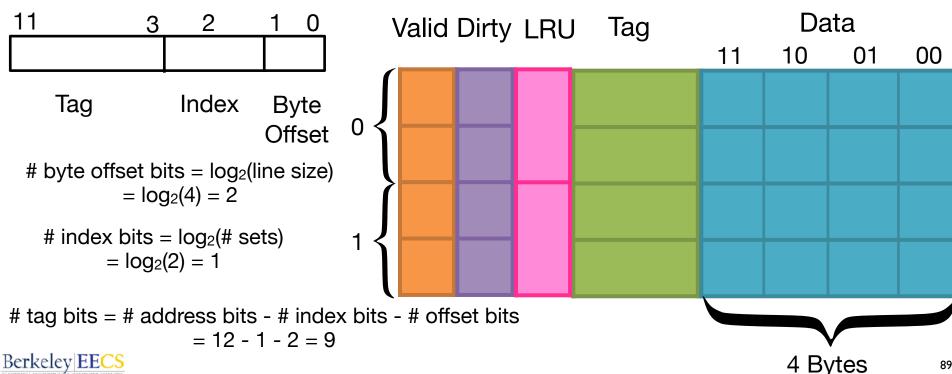

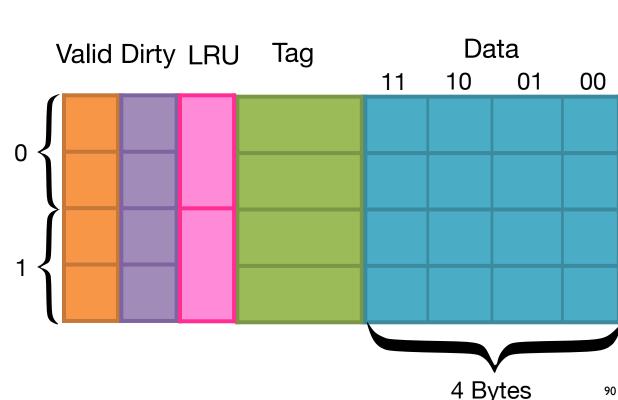

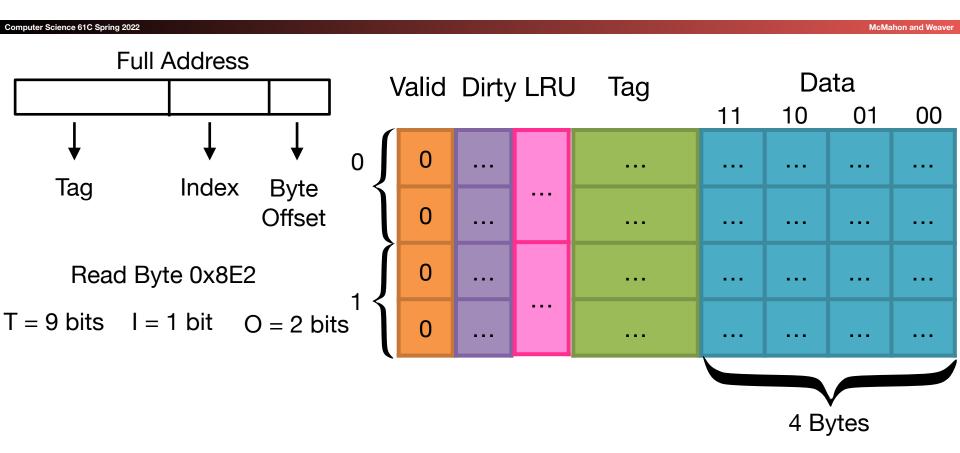

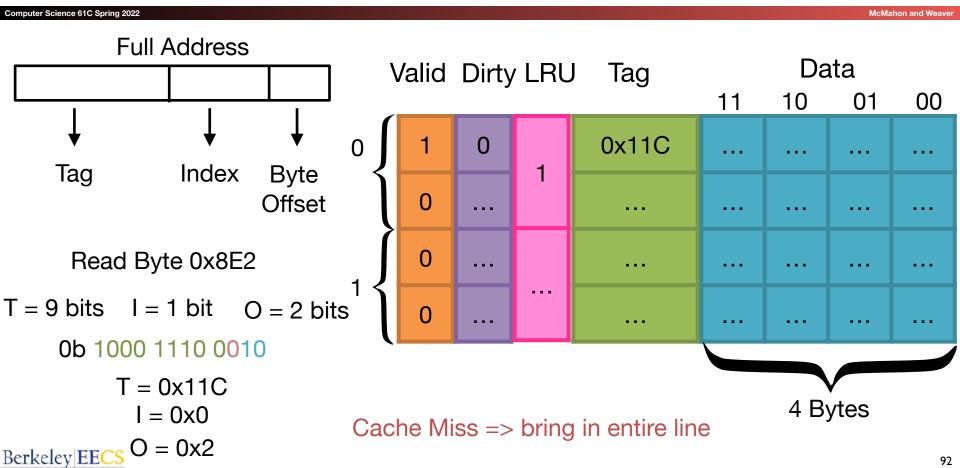

The data can only be stored at one index, but there are multiple slots to store it in Full Address: ex: 12 bits

The data can only be stored at one index, but there

are multiple slots

Computer Science 61C Spring 2022

to store it in

The LRU bit indicates which set has was least recently used

McMahon and Weaver

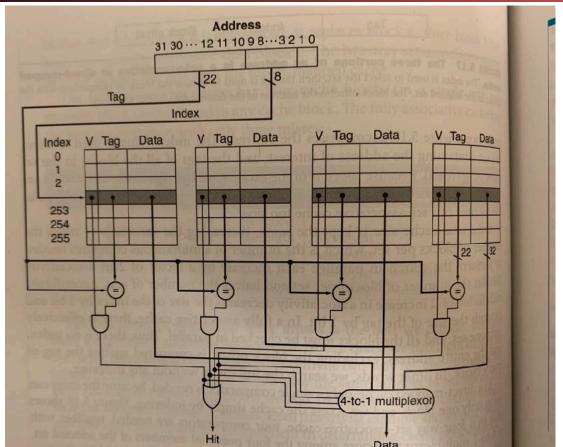

### Implementation of 4-way Set Associative Cache

Computer Science 61C Spring 2022 McMahon and Weaver

#### Types of Misses

Computer Science 61C Spring 2022

#### Compulsory Miss

Caused by the first access to a block that has never been in the cache

#### Capacity Miss

- Caused when the cache cannot contain all the blocks needed during the execution of a program

- Occur when blocks were in the cache, replaced, and later retrieved

#### Conflict Miss

- Occur in set-associative or direct mapped caches when multiple blocks compete for the same set

- Misses of this type would not occur in a fully associative cache of the same type

#### Comparisons

Computer Science 61C Spring 2022 McMahon and Weaver

#### Fully Associative

- A specific line of data can be stored in any line of the cache

- No index

- Need to choose replacement policy

#### Direct Mapped

- A specific line of data can only be stored in one index of the cache

- Has index

- If the line you want to store the data in is occupied, you kick out that line

#### Set Associative

- A specific line of data can be stored at only one index of the cache (but multiple lines can be in each index)

- Has index

- Need to choose replacement policy

#### **Next Lecture**

Computer Science 61C Spring 2022

McMahon and Weaver

- Cache Performance

- Multilevel Caches